# CS1232 用户手册

24-bit Sigma-Delta ADC

Rev 1.5

通讯地址:深圳市南山区蛇口南海大道 1079 号花园城数码大厦 A 座 9 楼

邮政编码: 518067

公司电话: +(86 755)86169257 传 真: +(86 755)86169057 公司网站: www.chipsea.com

微信号: 芯海科技

微信二维码:

# 版本历史

| 历史版本    | 修改内容                                | 版本日期       |

|---------|-------------------------------------|------------|

| REV 1.0 | 初始版本                                | 2011-08-25 |

| REV 1.1 | 更改时钟说明,增加温度传感器说明                    | 2011-09-20 |

| REV 1.2 | 更改封装资料                              | 2011-11-30 |

| REV 1.3 | 更改电气特性表                             | 2012-05-20 |

| REV 1.4 | 修改读取 AD 值的时序: 第 25 个 SCLK 将 DRDY 拉高 | 2012-07-09 |

| REV 1.5 | 更换新 LOGO,重新发布                       | 2014-10-17 |

|         |                                     |            |

|         |                                     |            |

|         |                                     |            |

|         |                                     |            |

# 目 录

| 版 | 本历史   |                                                         | 2  |

|---|-------|---------------------------------------------------------|----|

| 月 | 录     |                                                         | 3  |

| 1 | 芯片功能  | · 说明                                                    | 5  |

|   | 1.1   | 芯片主要功能特性                                                | 5  |

|   | 1.2   | 芯片应用场合                                                  |    |

|   | 1.3   | 芯片基本结构功能描述                                              |    |

|   | 1.4   | 芯片最大极限值                                                 |    |

|   | 1.5   | 数字逻辑特性                                                  | 8  |

|   | 1.6   | 电气特性                                                    | 9  |

|   | 1.7   | 噪声性能                                                    | 11 |

|   | 1.8   | 芯片引脚                                                    | 12 |

| 2 | 芯片功能  | 模块描述                                                    | 13 |

|   | 2.1   | 模拟输入前端                                                  | 13 |

|   | 2.2   | 温度传感器                                                   |    |

|   | 2.3   | 低噪声 PGA 放大器                                             | 15 |

|   | 2.4   | 时钟信号源                                                   | 16 |

|   | 2.5   | 复位和断电(POR & power down)                                 | 16 |

|   | 2.6   | SPI 串口通信                                                |    |

|   | 2.6.1 | 建立时间                                                    | 17 |

|   | 2.6.2 | 输出速率                                                    | 18 |

|   | 2.6.3 | 数据格式                                                    | 18 |

|   | 2.6.4 | 数据准备/数据输入输出( $\overline{\textit{DRDY}}/\textit{DOUT}$ ) | 19 |

|   | 2.6.5 | 串行时钟输入(SCLK)                                            | 19 |

|   | 2.6.6 | 数据接收                                                    | 20 |

|   | 2.6.7 | Standby 模式                                              | 21 |

|   | 2.6.8 | 上电顺序                                                    | 21 |

|   | 2.6.9 | Power down 模式                                           | 21 |

| 3 | 芯片封装  |                                                         | 23 |

# 图目录

| 图 1 CS1232 原理框图                    | 6  |

|------------------------------------|----|

| 图 2 CS1232 芯片引脚图                   | 12 |

| 图 3 模拟输入结构图                        | 13 |

| 图 4 PGA 结构图                        | 15 |

| 图 5 CS1232 时钟信号                    | 16 |

| 图 6 改变 A0 或 TEMP 引脚输入后的建立时间图       | 17 |

| 图 7 CS1232 在连续转换模式的建立时间            | 18 |

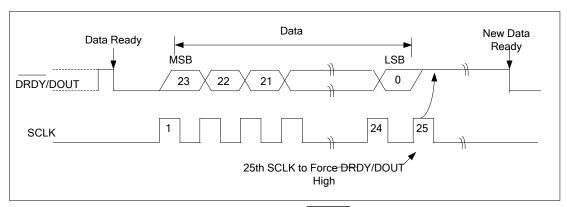

| 图 8 CS1232 读取数据时序图                 | 20 |

| 图 9 CS1232 读取数据时序且将 DRDY/DOUT 拉高时序 | 20 |

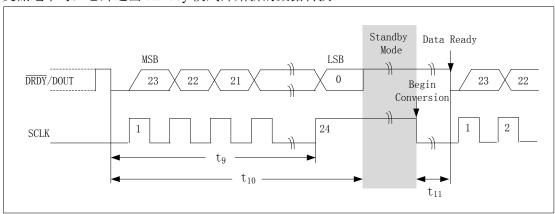

| 图 10 Standby 模式时序图                 |    |

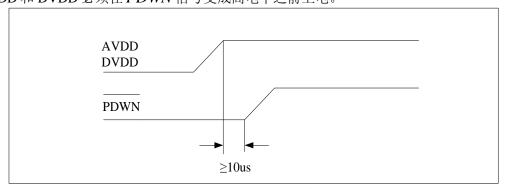

| 图 11 CS1232 上电顺序图                  |    |

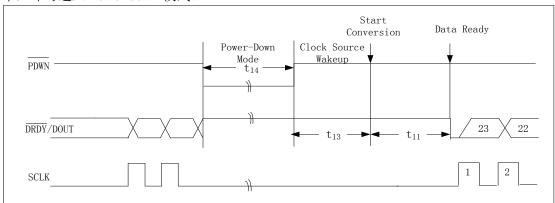

| 图 12 Power Down 模式时序图              | 22 |

| 图 13 芯片 TSSOP-24 封装尺寸信息            | 23 |

|                                    |    |

|                                    |    |

| 表目录                                |    |

| 表 1 CS1232 极限值                     |    |

| 表 2 CS1232 数字逻辑特性                  |    |

| 表 3 CS1232 电气特性(AVDD = DVDD = 5V ) |    |

| 表 4 CS1232 电气特性(AVDD = DVDD = 3V)  |    |

| 表 5 噪声性能表                          |    |

| 表 6 PIN 脚说明                        |    |

| 表7建立时间时序图                          |    |

| 表 8 输出速率设置                         |    |

| 表9理想输出码和输入信号(1)                    |    |

| 表 10 读取数据时序表                       | 20 |

| 表 11 Standby 模式时序表                 |    |

| 表 12 Power Down 模式时序表              | 22 |

# 1 芯片功能说明

CS1232是高精度、低功耗模数转换芯片。其分辨率为24bit,有效分辨率可达20.8位。可以 广泛使用在工艺控制、量重、液体/气体化学分析、血液分析、智能发送器、便携测量仪器 领域

### 1.1 芯片主要功能特性

- 集成低噪声 PGA, 放大倍数可选 1, 2, 64, 128

- 集成 2 通道 24 位无失码的差分输入 ADC, PGA=128 时 ENOB 为 20.8 位

- P-P 噪声: 10Hz: 139nV; 80Hz: 298nV

- 集成 RC 振荡器(±8%),也可外接晶振或时钟输入

- 输出速率 10Hz/80Hz 可选

- 集成 2 线 SPI 通讯接口

- 集成温度传感器

- INL 小于 0.001%

### 1.2 芯片应用场合

- 工业过程控制

- 电子秤

- 液体/气体化学分析

- 血液计

- 智能变换器

- 便携式设备

### 1.3 芯片基本结构功能描述

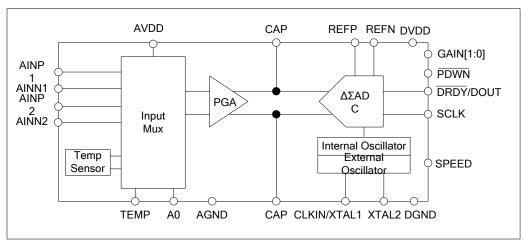

CS1232 是一款高精度、低功耗 Sigma-Delta 模数转换芯片,内置 1 路 Sigma-Delta ADC。ADC 采用三阶 Sigma-Delta 调制器,通过低噪声仪用放大器结构实现 PGA 放大,放大倍数可选 1, 2, 64, 128。在 PGA=128 时,有效分辨率可达 20.8 位。CS1232 输出速率 10Hz/80Hz 可选。CS1232 内置 RC 振荡器,可以使用外置晶振,也可以通过引脚 CKIN/XTAL1 直接输入时钟。CS1232 具有 Standby、Power down等更低功耗模式。

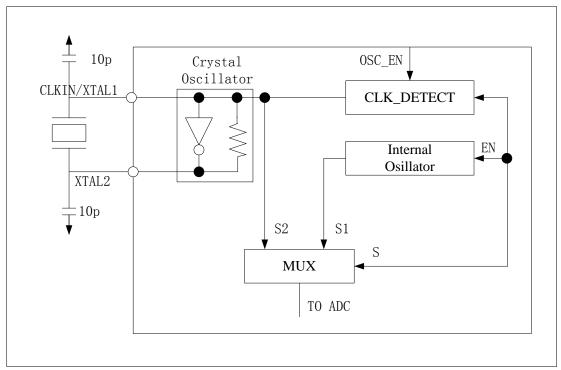

图1 CS1232 原理框图

# 1.4 芯片最大极限值

表1 CS1232 极限值

| 名称          | 符号   | 最小   | 最大       | 单位           |

|-------------|------|------|----------|--------------|

| 模拟电源电压      | AVDD | -0.3 | 6        | V            |

| 数字电源电压      | DVDD | -0.3 | 6        | V            |

| 数字地与模拟地之间压差 |      | -0.3 | 0.3      | V            |

| 电源瞬间电流      |      |      | 100      | mA           |

| 电源恒定电流      |      |      | 10       | mA           |

| 数字管脚输入电压    |      | -0.3 | DVDD+0.3 | V            |

| 模拟管脚输入电压    |      | -0.3 | AVDD+0.3 | V            |

| 节温          |      |      | 150      | $^{\circ}$   |

| 工作温度        |      | -40  | 105      | $^{\circ}$ C |

| 储存温度        |      | -60  | 150      | $^{\circ}$   |

| 芯片管脚焊接温度    |      |      | 240      | $^{\circ}$   |

# 1.5 数字逻辑特性

表2 CS1232 数字逻辑特性

| 参数                        | 最小       | 典型     | 最大       | 单位  | 条件说明    |

|---------------------------|----------|--------|----------|-----|---------|

| VIH                       | 0.7×DVDD |        | DVDD+0.1 | V   |         |

| VIL                       | DGND     |        | 0.3×DVDD | V   |         |

| VIH (PWDN)                | 0.8×DVDD |        | DVDD+0.1 | V   |         |

| VIL (PWDN)                | DGND     |        | 0.2×DVDD | V   |         |

| VOH                       | DVDD-0.4 |        | DVDD     | V   | Ioh=1mA |

| VOL                       | DGND     |        | 0.2×DVDD | V   | IoL=1mA |

| IIH                       |          |        | 10       | uA  | VI=DVDD |

| IIL                       | -10      |        |          | uA  | VI=DGND |

| 外置时钟工作频率范围 <sup>(1)</sup> | 0.2      | 4.9152 | 8        | MHz |         |

| 串口时钟工作频率范围(2)             |          |        | 2        | MHz |         |

- (1) 芯片工作时钟频率

- (2) 串口通信时钟SCLK的频率

# 1.6 电气特性

所有的参数测试在环境温度-20~85℃,AVDD = DVDD = 5V,REFP = 5V,REFN = 0V 的条件下测试,除非有其它注明。

表3 CS1232 电气特性 (AVDD = DVDD = 5V)

|                                             | 条件               | 最小值          | 典型值          | 最大值         | 单位                                    |

|---------------------------------------------|------------------|--------------|--------------|-------------|---------------------------------------|

|                                             | 411              | →X√1,旧       | 八王           | 八八山         | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|                                             |                  | I            | T T          |             | <u> </u>                              |

| 满幅输入电压<br>(AINP-AIN)                        |                  |              | ±0.5VREF/PGA |             | V                                     |

|                                             | PGA=1, 2         | AGND-0.1     |              | AVDD+0.1    | V                                     |

| 共模输入电压                                      | PGA=64, 128      | AGND+1.5     |              | AVDD-1.5    | V                                     |

| 共模电压抑制比                                     | 10/1-04, 120     | TIGIND   1.5 | 125          | 11100 1.5   | dB                                    |

| <u> </u>                                    | PGA=64, 128      |              | >1           |             | GΩ                                    |

| 差分输入阻抗                                      | PGA=1, 2         |              | >1           |             | GΩ                                    |

| 系统性能                                        | 10/1-1\ 2        |              |              |             | 032                                   |

| 分辨率                                         | 无失码              |              | 24           |             | Bits                                  |

| AD速率                                        | 时钟为4.9152MHz     |              | 10           | 80          | Hz                                    |

| 建立时间                                        | 全建立              |              | 4            | 00          | 转换周期                                  |

| P-P噪声                                       | PGA=128, DR=10Hz |              | 139          |             | nV                                    |

| 积分线性度                                       | PGA=128          |              | ±6           |             | ppm                                   |

| 失调误差                                        | PGA=128          |              | -1           |             | uV                                    |

| 失调误差漂移                                      | PGA=128          |              | 25           |             | nv/°C                                 |

| 增益误差                                        | PGA=128          |              | ±0.1         |             | %                                     |

| 增益误差漂移                                      | PGA=128          |              | 6            |             | ppm/°C                                |

| 参考电压输入                                      | 1 0/1-120        |              |              |             | ррш/ С                                |

| 负参考电压输入                                     | REFN             | AGND-0.1     |              | AGND+0.6    | V                                     |

| 正参考电压输入                                     | REFP             | REFN +2.5    |              | AVDD+0.1    | V                                     |

| REFP — REFN                                 | TALL I           | 2.5          | AVDD         | AVDD+0.1    | V                                     |

| 参考电压抑制比                                     |                  | 2.3          | 54           | 11,122,1011 | dB                                    |

| 电源                                          |                  |              | <u> </u>     |             |                                       |

| 模拟电源电压                                      | AVDD             | 2.8          | 5            | 5.5         | V                                     |

| 数字电源电压                                      | DVDD             | 2.8          | 5            | 5.5         | V                                     |

|                                             | PGA=1, 2         |              | 90           |             | dB                                    |

| 电源电压抑制比                                     | PGA=64, 128      |              | 110          |             | dB                                    |

|                                             | 普通 PGA=1、2       |              | 2            |             | mA                                    |

| + + 1 4 4 7 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 模式 PGA=64、128    |              | 3            |             | mA                                    |

| 模拟部分电流                                      | Standby mode     |              | 6            |             | uA                                    |

|                                             | Power down       |              | 0.1          |             | uA                                    |

|                                             | normal mode      |              | 400          |             | uA                                    |

| 数字部分电流                                      | Standby mode     |              | 150          |             | uA                                    |

| w t. & t.                                   | Power down       |              | 1.5          |             | uA                                    |

| 时钟                                          | I                | 1            |              |             |                                       |

| 内部振荡器频率                                     |                  | 4.6          | 5            | 5.4         | MHz                                   |

| 内置时钟温漂                                      |                  |              | 250          |             | ppm/℃                                 |

| 外部时钟频率                                      |                  | 0.2          | 4.9152       | 8           | MHz                                   |

所有的参数测试在环境温度-20~85℃,AVDD = DVDD = 3V,REFP = 3V,REFN = 0V 的条件下测试,除非有其它注明。

表4 CS1232 电气特性 (AVDD = DVDD = 3V)

| 参数            | 1        | 条件                   | 最小值         | 典型值          | 最大值      | 单位     |

|---------------|----------|----------------------|-------------|--------------|----------|--------|

| 模拟输入          |          | A-11                 | W 1 E       | 八工匠          |          | 7 744  |

| 满幅输入电压        |          |                      |             | 0.51105500.4 |          |        |

| (AINP-AIN)    |          |                      | 0.5VREF/PGA |              |          | V      |

| +++++-> +-    | PC       | GA=1, 2              | AGND-0.1    |              | AVDD+0.1 | V      |

| 共模输入电压        | PGA      | =64, 128             | AGND+1.5    |              | AVDD-1.5 | V      |

| 共模电压抑制比       |          |                      |             | 125          |          | dB     |

| <b>光八松)四长</b> | PGA      | =64、128              |             | >1           |          | GΩ     |

| 差分输入阻抗        | PC       | GA=1, 2              |             | >1           |          | GΩ     |

| 系统性能          |          |                      |             |              |          |        |

| 分辨率           | =        | 无失码                  |             | 24           |          | Bits   |

| AD速率          | 时钟为      | J4.9152MHz           |             | 10           | 80       | Hz     |

| 建立时间          | 3        | 全建立                  |             | 4            |          | 转换周期   |

| P-P噪声         | PGA=12   | 28, DR=10Hz          |             | 145          |          | nv     |

| 积分线性度         | PC       | GA=128               |             | ±6           |          | ppm    |

| 失调误差          | PC       | GA=128               |             | -1           |          | uV     |

| 失调误差漂移        | PC       | GA=128               |             | 25           |          | nv/℃   |

| 增益误差          | PC       | GA=128               |             | ±0.1         |          | %      |

| 增益误差漂移        | PC       | GA=128               |             | 6            |          | ppm/°C |

| 参考电压输入        |          |                      |             |              |          |        |

| 负参考电压输入       | ,        | REFN                 | AGND-0.1    |              | AGND+0.6 | V      |

| 正参考电压输入       |          | REFP                 | REFN +1.5   |              | AVDD+0.1 | V      |

| REFP — REFN   |          |                      | 1.5         | AVDD         | AVDD+0.1 | V      |

| 参考电压抑制比       |          |                      |             | 54           |          | dB     |

| 电源            |          |                      |             |              |          |        |

| 模拟电源电压        | I        | AVDD                 | 2.8         | 5            | 5.5      | V      |

| 数字电源电压        | I        | DVDD                 | 2.8         | 5            | 5.5      | V      |

| 电源电压抑制比       | PGA=1, 2 |                      |             | 90           |          | dB     |

| 电源电压抑制比       | PGA      | =64、128              |             | 110          |          | dB     |

|               | 普通       | PGA=1、2              |             | 1.8          |          | mA     |

| 模拟部分电流        | 模式       | PGA=64、128           |             | 2.7          |          | mA     |

| 大场的为 电机       |          | dby mode             |             | 3            |          | uA     |

|               |          | wer down             |             | 0.1          |          | uA     |

| 华启动八十岁        |          | mal mode             |             | 360          |          | uA     |

| 数字部分电流        |          | dby mode<br>wer down |             | 100<br>1.5   |          | uA     |

| 时钟            | F0\      | wei dowii            |             | 1.3          |          | uA     |

| 内部振荡器频率       |          |                      | 4.4         | 5            | 5.6      | MHz    |

| 内置时钟温漂        |          |                      | 7.4         | 250          | 3.0      | ppm/°C |

| 外部时钟频率        |          |                      | 0.2         | 4.9152       | 8        | MHz    |

| 7丁目PPT 7丁/2火午 | 1        |                      | 0.2         | 4.7134       | O        | MILIT  |

# 1.7 噪声性能

表5 噪声性能表

| 条件      | 速度   | 増益  | RMS 噪声 | P-P 噪声  | ENOB(RMS) | NOISE-FREE BITS |

|---------|------|-----|--------|---------|-----------|-----------------|

|         |      | 1   | 400nV  | 1.69uV  | 23.6      | 21.5            |

|         | 10HZ | 2   | 278nV  | 900nV   | 23.1      | 21.4            |

|         | 10nZ | 64  | 23nV   | 149nV   | 21.7      | 19.0            |

| AVDD=5V |      | 128 | 21nV   | 139nV   | 20.8      | 18.1            |

| VREF=5V |      | 1   | 1.57uV | 9.53uV  | 21.6      | 19              |

|         | 80HZ | 2   | 903nV  | 5.87uV  | 21.4      | 18.7            |

|         |      | 64  | 56nV   | 342nV   | 20.4      | 17.8            |

|         |      | 128 | 56nV   | 298nV   | 19.4      | 17              |

|         | 10HZ | 1   | 334nV  | 2.02uV  | 23.1      | 20.5            |

|         |      | 2   | 291nV  | 1.43uV  | 22.3      | 20              |

|         |      | 64  | 26nV   | 167nV   | 20.8      | 18.1            |

| AVDD=3V |      | 128 | 23nV   | 145nV   | 20.0      | 17.3            |

| VREF=3V |      | 1   | 2.02uV | 11.44uV | 20.5      | 18              |

|         | 80HZ | 2   | 943nV  | 5.34uV  | 20.6      | 18.1            |

|         | OUHZ | 64  | 63nV   | 383nV   | 19.5      | 16.9            |

|         |      | 128 | 67nV   | 358nV   | 18.4      | 16              |

# 1.8 芯片引脚

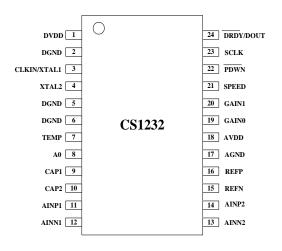

图2 CS1232 芯片引脚图

表6 PIN 脚说明

| 序号 | 引脚名称                   | 输入/输出 | 说明                                    |           |                 |  |  |

|----|------------------------|-------|---------------------------------------|-----------|-----------------|--|--|

| 1  | DVDD                   | P     | 数字电源                                  |           |                 |  |  |

| 2  | DGND                   | P     | 数字地                                   |           |                 |  |  |

| 3  | CLKIN/XTAL1            | DI    | 外置晶振端口, 同                             | 可提供外部时钟输  | 俞入              |  |  |

| 4  | XTAL2                  | DI    | 外置晶振端口                                |           |                 |  |  |

| 5  | DGND                   | P     | 数字地                                   |           |                 |  |  |

| 6  | DGND                   | P     | 数字地                                   |           |                 |  |  |

| 7  | TEMP                   | DI    | 内部温度传感器控制: 0: 不使能; 1: 使能              |           |                 |  |  |

| 8  | A0                     | AI    | 通道选择: 0: 选择通道1; 1: 选择通道2              |           |                 |  |  |

| 9  | CAP1                   | AI    | DCA 故士舉輪山                             | CAD1 CAD2 | 之间处按 O 1 n E 由家 |  |  |

| 10 | CAP2                   | AI    | PGA 放大器输出,CAP1、CAP2 之间外接 0.1uF 电容     |           |                 |  |  |

| 11 | AINP1                  | AI    | 通道1正输入                                |           |                 |  |  |

| 12 | AINN1                  | AI    | 通道1负输入                                |           |                 |  |  |

| 13 | AINN2                  | AI    | 通道2负输入                                |           |                 |  |  |

| 14 | AINP2                  | AI    | 通道2正输入                                |           |                 |  |  |

| 15 | REFN                   | AI    | 参考电压负端输入                              |           |                 |  |  |

| 16 | REFP                   | AI    | 参考电压正端输入                              | \         |                 |  |  |

| 17 | AGND                   | P     | 模拟地                                   |           |                 |  |  |

| 18 | AVDD                   | P     | 模拟电源                                  |           |                 |  |  |

| 19 | GAIN0                  | AI    | PGA 选择<br>GAIN1<br>0                  | GAIN0     | GAIN            |  |  |

|    |                        |       | 0                                     | 1         | 2               |  |  |

| 20 | GAIN1                  | AI    | 1                                     | 0         | 64              |  |  |

|    |                        | 1     |                                       | 1         | 128             |  |  |

| 21 | SPEED                  | DI    | 输出速率选择:<br>speed=0,10Hz; speed=1,80Hz |           |                 |  |  |

| 22 | $\overline{PWDN}$      | DI    | power down 控制端口(低电平有效)                |           |                 |  |  |

| 23 | SCLK                   | DI    | SPI 时钟输入端口                            |           |                 |  |  |

| 24 | $\overline{DRDY}/DOUT$ | DO    | SPI 数据输入/输出                           |           |                 |  |  |

# 2 芯片功能模块描述

# 2.1 模拟输入前端

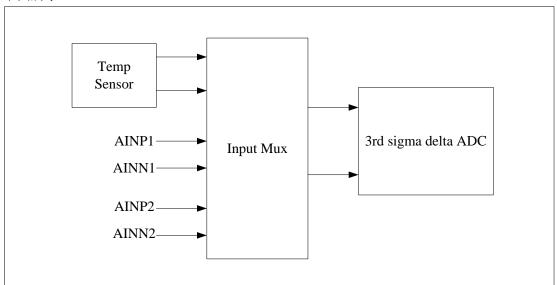

CS1232 中有 1 路 ADC,集成 2 通道差分输入,信号输入可以是差分输入信号 AINP1、AINN1 或 AINP2、AINN2,也可以切换到温度传感器的输出信号。AINP1、AINN1 或 AINP2、AINN2 的切换由 A0 控制,温度传感器的切换由 TEMP 引脚控制。其基本结构如下图所示:

图3 模拟输入结构图

### 2.2 温度传感器

芯片内部提供温度测量功能。当 PIN 脚 TEMP 接高电平时,ADC 模拟信号输入接到内部温度传感器,其它的模拟输入信号无效。ADC 通过测量内部温度传感器输出的电压差来推导出实际的温度值。当 TEMP=1 时,ADC 只支持 PGA=1 和 PGA=2。当引脚 GAIN0=0,

TEMP=1,此时测温度传感器的 PGA=1。当引脚 GAIN0=1,TEMP=1,此时测温度传感器的 PGA=2。

温度传感器需要进行单点校正。校正方法: 在某个温度点 A 下,使用温度传感器进行测量得到码值 Ya。

那么其他温度点 B 对应的温度= Yb\*(273.15+A)/Ya-273.15

A温度单位是摄氏度。Ya是A点对应温度码值。Yb是B点对应温度码值。

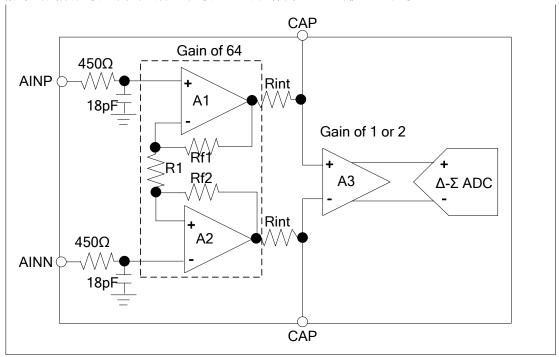

### 2.3 低噪声 PGA 放大器

CS1232 集成低噪声,低漂移 PGA 放大器与桥式传感器差分输出连接,其内部基本结构如图 4 所示,前置抗 EMI 滤波器电路 R=450Ω,C=18pF 实现 20M 高频滤波。低噪声 PGA 放大器通过 RF1,R1,RF2 实现 64 倍放大,与后级电路组成 64 和 128 的 PGA 放大。通过对引脚 GAIN1,GAIN0 的控制来选择 1 倍,2 倍,64 倍,128 倍等不同的增益倍数。当使用 PGA=1,2 时,64 倍低噪声 PGA 放大器会被关断以节省功耗。在 CAP 端口处接一个外置 0.1uF 电容,与内置 2K 欧电阻 RINT 组成一个低通滤波电路,用于低噪声 PGA 放大器输出信号的高频滤波,同时该低通滤波器也可以作为 ADC 的抗混叠滤波器。

图4 PGA 结构图

### 2.4 时钟信号源

图5 CS1232 时钟信号

CS1232 可以使用外部输入时钟、外置晶振或内置振荡电路来提供系统所需要的时钟频率,图 5 为 CS1232 时钟系统的基本结构图,CLK\_DETECT 用来检测是否存在外置时钟以确定关闭或打开内置振荡电路,当 CLKIN/XTAL1 的频率超过 200kHz 时,CLK\_DETECT 的输出置低以关闭内置振荡电路,当 CLKIN/XTAL1 的频率小于 200kHz 时,CLK\_DETECT 的输出置高以打开内置振荡电路,使用内置振荡电路建议将 CLKIN/XTAL1 置低。

当使用外置晶振时,晶振连接到引脚 CLKIN/XTAL1 和 XTAL2,并在 CLKIN/XTAL1 和 XTAL2 引脚连接 10p 到地电容。

#### 2.5 复位和断电(POR & power down)

当芯片上电时,内置上电复位电路会使芯片自动复位。将引脚 $\overline{PDWN}$ 端口拉低,可以使整个系统进入 $\overline{PDWN}$ 拉高。

#### 2.6 SPI 串口通信

CS1232 采用 2 线 SPI 串口通信,通过 SCLK 和  $\overline{DRDY}/DOUT$  可以实现数据的接收。 CS1232 可以持续的转换模拟输入信号,当将  $\overline{DRDY}/DOUT$  拉低后,表明数据已经准备 好,输入的第一个 SCLK 就可以将 24 位 AD 值的最高位读出,在 24 个 SCLK 后,将所有 的 24 位 DOUT 数据读出,之后  $\overline{DRDY}/DOUT$  会保持着最后一位的数据,直到下一个数据准备好之前拉高,此后当  $\overline{DRDY}/DOUT$  被再次拉低,表示新的数据已经转换完成,可 进行下一个数据读取。在接收完成一组数据后,应当保持 SCLK 的电平为低,防止 SCLK 高电平时间过长,使 CS1232 误入 Standby 模式。每次数据读取可以不需要读完 24bit 数据,是否全部读完 24bit 数据对下次模数转换没有影响。

#### 2.6.1 建立时间

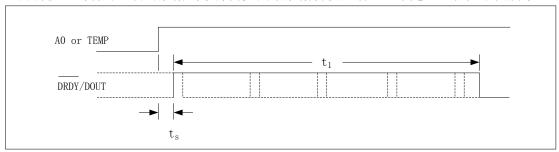

数字部分需要有四个数据转换周期满足模拟输入信号的建立和滤波器的建立时间要求。芯片从外部差分输入信号切换到温度传感器、从温度传感器切换到外部差分输入信号,或通道间切换,到新的正确的数据到来都需要四个数据转换周期。整个建立过程如下图所示:

图6 改变 A0或 TEMP 引脚输入后的建立时间图

描述<sup>(1)</sup> 参数 最大值 单位 最小值 改变 A0 或 TEMP 后的建立时间 ts 40 50 us SPEED = 157 57 ms 建立时间(DRDY/DOUT保持高电 t1 SPEED = 0407 407 ms 平)

表7 建立时间时序图

(1)值是在 fclk=4.9152MHz 时对应的值,不同的 fclk 频率,数值等比例变化。

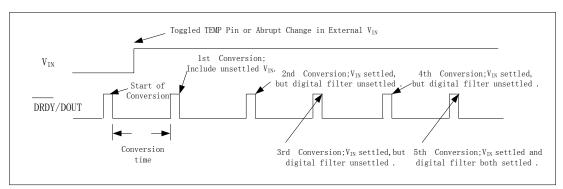

CS1232 在连续转换过程中,若外部差分输入信号发生突然变化,同样需要建立时间。突变的信号需要 4 个转换周期进行建立,第 5 个转换周期得到最终的 AD 值。图 7 描述突变信号建立的过程。若在建立的过程中,信号再发生突变,则忽略之前的建立,需要新的 4 个转换周期进行建立,之后紧接着的第 5 个转换周期得到最终的 AD 值。

图7 CS1232 在连续转换模式的建立时间

#### 2.6.2 输出速率

CS1232 的输出速率可以通过 SPEED 引脚设置。当 SPEED 为低电平时,输出速率为 10Hz,此时输出速率拥有最小的噪声,并对 50Hz/60Hz 噪声有很好的抑制作用;当 SPEED 为高电平时,输出速率为 80Hz。

| SPEED 引脚  | 输出速率          |                           |  |  |  |

|-----------|---------------|---------------------------|--|--|--|

| SPEED 5 M | 时钟为 4.9152MHz | 外部时钟                      |  |  |  |

| 0         | 10Hz          | f <sub>CLK</sub> /491,520 |  |  |  |

| 1         | 80Hz          | $f_{CLK}/61,440$          |  |  |  |

表8 输出速率设置

#### 2.6.3 数据格式

CS1232 输出的数据为 24 位的 2 进制补码,最高位(MSB)最先输出。最小有效位 (LSB) 为(0.5V<sub>REF</sub>/Gain)/(2<sup>23</sup>-1)。正值满幅输出码为 7FFFFFH,负值满幅输出码为 800000H。下表为不同模拟输入信号对应的理想输出码。

|                                  | 秋/ 经心物山内/h-榆/八百 J |  |  |  |  |  |  |  |

|----------------------------------|-------------------|--|--|--|--|--|--|--|

| 输入信号 V <sub>IN</sub> (AINP-AINN) | 理想输出              |  |  |  |  |  |  |  |

| ≥+0.5V <sub>REF</sub> /Gain      | 7FFFFH            |  |  |  |  |  |  |  |

| $(+0.5V_{REF}/Gain)/(2^{23}-1)$  | 000001H           |  |  |  |  |  |  |  |

| 0                                | 000000Н           |  |  |  |  |  |  |  |

| $(-0.5V_{REF}/Gain)/(2^{23}-1)$  | FFFFFH            |  |  |  |  |  |  |  |

| ≤+0.5V <sub>REF</sub> /Gain      | 800000Н           |  |  |  |  |  |  |  |

表9 理想输出码和输入信号(1)

(1) 不考虑噪声, INL, 失调误差和增益误差的影响

## **2.6.4** 数据准备/数据输入输出( $\overline{DRDY}/DOUT$ )

DRDY/DOUT 引脚有 2个用途。第一,当输出为低时,表示新的数据已经转换完成;第二,作为数据输出引脚,当数据准备好后,在第 1个 SCLK 的上升沿后, $\overline{DRDY}/DOUT$  输出转换数据的最高位(MSB)。在每一个 SCLK 的上升沿,数据会自动移 1 位。在 24 个 SCLK 后,将所有的 24 位 DOUT 数据读出,之后  $\overline{DRDY}/DOUT$  会保持着最后一位的数据,直到下一个数据准备好之前拉高,此后当  $\overline{DRDY}/DOUT$  被再次拉低,表示新的数据已经转换完成,可进行下一个数据读取。

#### 2.6.5 串行时钟输入(SCLK)

串行时钟输入是一个数字引脚。这个信号应保证是一个干净的信号,毛刺或慢速的上升沿都会可能导致读取错误数据或误入错误状态。因此,应保证 SCLK 的上升和下降时间都小于 50ns。

#### 2.6.6 数据接收

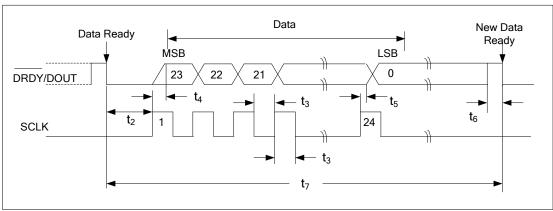

CS1232 可以持续的转换模拟输入信号,当将 DRDY/DOUT 拉低后,表明数据已经准备好接受,输入的第一个 SCLK 来就可以将输出的最高位读出,在 24 个 SCLK 后,将所有的 24 位 DOUT 数据读出,之后 DRDY/DOUT 会保持着最后一位的数据,直到其被拉高,通过第 25 个 SCLK 可以将 DRDY/DOUT 拉高,此后当 DRDY/DOUT 被再次拉低,表示新的数据已经准备好接受,进行下一个数据的转换。其基本时序如图所示:

图8 CS1232 读取数据时序图

图9 CS1232 读取数据时序且将 DRDY/DOUT 拉高时序

|        | * * * * * * * * * * * * * * * * * * * * |           |     |      |     |       |

|--------|-----------------------------------------|-----------|-----|------|-----|-------|

| SYMBOL | DESCRIPTION                             |           | MIN | TYP  | MAX | UNITS |

| t2     | DRDY/DOUT 变低后到第一个SCLK上升<br>沿            |           | 0   |      |     | ns    |

| t3     | SCLK 高电平或低电平脉宽                          |           | 250 |      |     | ns    |

| t4     | SCLK上升沿到新数据位有效(传输延迟)                    |           |     |      | 200 | ns    |

| t5     | SCLK上升沿到旧数据位有效(保持时间)                    |           | 0   |      |     | ns    |

| t6     | 数据更新, 不允许读之前的数据                         |           | 39  |      |     | us    |

| t7     | <del>转</del> 拖时间 (1/data rata)          | SPEED = 1 |     | 12.5 |     | ms    |

| t/     | 转换时间 (1/data rate) SPEED = 0            |           |     | 100  |     | ms    |

表10 读取数据时序表

#### 2.6.7 Standby 模式

Standby 模式通过关闭大部分电路来减小功耗。在 standby 模式中,整个模拟电路关闭,只有时钟电路工作。进入 standby 模式的方式是,  $\overline{\textit{DRDY}}/\textit{DOUT}$  变低后(数据准备好),

一直保持 SCLK 高电平即可进入 standby 模式。进入 standby 模式的方式是在任何读取数据过程中。当 SCLK 保持高电平满足 t10,Standby 模式将会激活。进入 standby 模式,

DRDY/DOUT 会保持高电平。在 standby 模式,SCLK 必须一直保持为高电平。当 SCLK 变低电平时,芯片退出 standby 模式开始新的数据转换。

图10 Standby 模式时序图

| 参数                 | 描述                                                       |           | 最小值   | 最大值   | 单位 |

|--------------------|----------------------------------------------------------|-----------|-------|-------|----|

| t9 <sup>(1)</sup>  | 在 <b>DRDY</b> / <b>DOUT</b> 变低后,<br>SCLK 拉高进入 standby 模式 | SPEED = 1 | 0     | 12.44 | ms |

|                    |                                                          | SPEED = 0 | 0     | 99.94 | ms |

| t10 <sup>(1)</sup> | standby 模式激活时间                                           | SPEED = 1 | 12.46 |       | ms |

|                    |                                                          | SPEED = 0 | 99.96 |       | ms |

| t11 <sup>(1)</sup> | 退出 standby 后到数据准备好                                       | SPEED = 1 | 57    | 57    | ms |

|                    |                                                          | SPEED = 0 | 407   | 407   | ms |

表11 Standby 模式时序表

(1) 值是在 fclk=4.9152MHz 时对应的值,不同的 fclk 频率,数值等比例变化

#### 2.6.8 上电顺序

AVDD 和 DVDD 必须在  $\overline{PDWN}$  信号变成高电平之前上电。

图11 CS1232 上电顺序图

#### 2.6.9 Power down 模式

$\overline{PDWN}$ 信号有效时关掉芯片所有电路,功耗小于 1.6uA。只需把  $\overline{PDWN}$  引脚保持低电平,即可进入 Power down 模式。

图12 Power Down 模式时序图

表12 Power Down 模式时序表

| 参数                 | 描述                   | 典型值  | 单位    |    |

|--------------------|----------------------|------|-------|----|

| t13 <sup>(1)</sup> | 在 POWER DOWN 模式下唤醒时间 | 内部时间 | 7.95  | us |

|                    |                      | 外部时间 | 0.16  | us |

|                    |                      | 晶振   | 5.6   | ms |

| t14 <sup>(1)</sup> | PDWN 脉宽              |      | 26    | us |

| 114                |                      |      | (min) |    |

(1) 值是在 fclk=4.9152MHz 时对应的值,不同的 fclk 频率,数值等比例变化

# 3 芯片封装

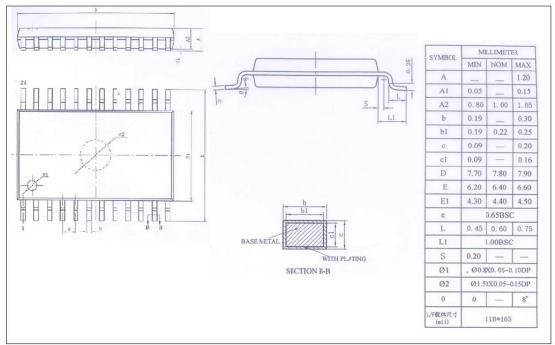

### 采用 TSSOP-24 封装

图13 芯片 TSSOP-24 封装尺寸信息