# NS4203 用户手册 V1.1

深圳市纳芯威科技有限公司 2013年5月

## 修改历史

| 日期        | 版本   | 作者 | 修改说明   |

|-----------|------|----|--------|

| 2013-5-30 | V1.1 |    | 去除耳机功能 |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

|           |      |    |        |

# 目 录

| 1  | 功能说明              |               | 5    |

|----|-------------------|---------------|------|

| 2  | 主要特性              | <u> </u>      | 5    |

| 3  | 应用领域              | <b>d</b>      | 5    |

| 4  | 典型应用              | ]电路           | 5    |

| 5  | 极限参数              |               | 6    |

| 6  | 电气特性              |               | 6    |

| 7  | 芯片管旗              | 『描述           | 7    |

|    | 7.1<br>7.2        | SOP16 封装管脚分配图 |      |

| 8  | NS4203            | 典型参考特性        | 8    |

| 9  | NS4203 )          | 应用说明          | . 11 |

| (  | 9.1<br>9.2<br>9.3 | 芯片基本结构描述      | . 12 |

| 9  | 9.4<br>9.5        | エモ, 洋モ朱戸      | . 12 |

| (  | 9.6               | 保护电路          |      |

| 10 | NS4203            | 应用注意事项        | . 13 |

| 11 | 芯片的               | 対装            | . 15 |

|    | 11 1              | SOP16 封装尺寸图   | 15   |

# 图目录

| 图 1 NS4203 典型应用电路           | 5  |

|-----------------------------|----|

| 图 2 SOP16 封装管脚分配图(top view) | 7  |

| 图 3 NS4203 原理框图             | 11 |

| 图 4 EMI 测试频谱图               | 13 |

| 图 5 NS4203 加磁珠应用电路          | 14 |

| 图 6 SOP16 封装尺寸图             | 15 |

|                             |    |

|                             |    |

| 表 目 录                       |    |

| 表 1 芯片最大物理极限值               | 6  |

| 表 2 NS4203 电气特性             | 6  |

| 表 3 NS4203 管脚描述             | 8  |

| 表 4 NS4203 工作模式设置           | 12 |

## 1 功能说明

NS4203 是一款超低 EMI、无需滤波器、3W 双声道 D类音频功放。NS4203 采用先进的技术,在全带宽范围内极大地降低了 EMI 干扰,最大限度地减少对其他部件的影响。NS4203 无需滤波器的 PWM 调制结构及反馈电阻内置方式减少了外部元件、PCB 面积和系统成本。NS4203 内置过流保护、过热保护及欠压保护功能,有效地保护芯片在异常工作状况下不被损坏。并且利用扩频技术充分优化全新电路设计,高达 85%的效率更加适合便携式音频产品。

NS4203 提供 SOP16 封装,额定的工作温度范围为-40℃至 85℃。

## 2 主要特性

- 3W 输出功率(10% THD、5V 电源、3Ω 负载)

- 0.2%THD+N(0.5W输出功率、5V电源)

- 优异的全带宽 EMI 抑制能力

- 优异的"上电,掉电"噪声抑制

- 高达 85%的效率

- 高 PSRR: -80dB (217Hz)

- 工作电压范围: 3.0V~5.25V

- 过流保护、过热保护、欠压保护

- SOP16 封装

## 3 应用领域

- 手提电脑

- 台式电脑

- 低压音响系统

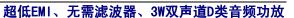

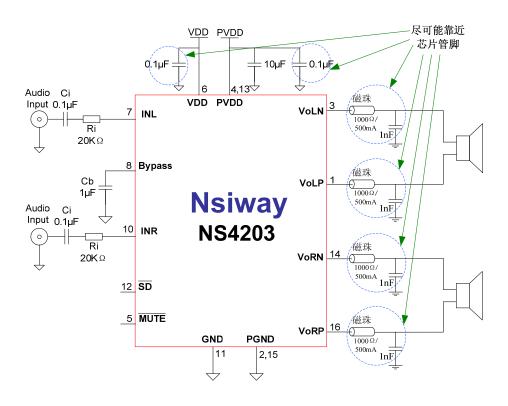

#### 4 典型应用电路

图1 NS4203 典型应用电路

# 5 极限参数

表1 芯片最大物理极限值

| 参数                      | 最小值  | 最大值      | 单位   | 说明    |

|-------------------------|------|----------|------|-------|

| 电源电压                    | 1.8  | 6        | V    |       |

| 储存温度                    | -65  | 150      | °C   |       |

| 输入电压                    | -0.3 | $V_{DD}$ | V    |       |

| 耐 ESD 电压                | 4000 |          | V    |       |

| 结温                      | 150  |          | °C   |       |

| 推荐工作温度                  | -40  | 85       | °C   |       |

| 推荐工作电压                  | 2.2  | 5.25     |      |       |

| 热阻                      |      |          |      |       |

| θ <sub>JC</sub> (SOP16) |      | 20       | °C/W |       |

| $\theta_{JA}(SOP16)$    |      | 80       | °C/W |       |

| 焊接温度                    |      | 220      | °C   | 15 秒内 |

注: 在极限值之外或任何其他条件下, 芯片的工作性能不予保证。

# 6 电气特性

限定条件: (TA=25℃)

表2 NS4203 电气特性

| 符号                | 参数           | 测试条件                                                          | 最小值 | 标准值 | 最大值  | 单位  |

|-------------------|--------------|---------------------------------------------------------------|-----|-----|------|-----|

| $V_{DD}$          | 电源电压         |                                                               | 3.0 |     | 5.25 | V   |

| T                 | 电源静态电流       | $V_{DD} = 3.6V$ , $V_{IN} = 0V$ , No load                     |     | 11  |      | mA  |

| $I_{DD}$          |              | $V_{DD} = 5.0V$ , $V_{IN} = 0V$ , No load                     |     | 20  |      | mA  |

| I <sub>MUTE</sub> | 待机电流         | $V_{DD} = 3.6V$ , $V_{IN} = 0V$<br>$V_{/MUTE} = 0V$ , No load |     | 8   |      | mA  |

| 1MUTE             |              | $V_{DD} = 5.0V$ , $V_{IN} = 0V$<br>$V_{/MUTE} = 0V$ , No load |     | 16  |      | mA  |

| $I_{SD}$          | 关断漏电流        | $V_{/SD} = 0V$                                                |     | 1   |      | μΑ  |

| $V_{OS}$          | 输出失调电压       |                                                               |     | 10  | 40   | mV  |

| $R_{O}$           | 输出电阻         |                                                               |     | 3   |      | ΚΩ  |

| PSRR              | 电源抑制比        | 217Hz                                                         |     |     | -80  | dB  |

| 1 SIXIX           |              | 20KHz                                                         |     |     | -72  | dB  |

| CMRR              | 共模抑制比        |                                                               |     | -70 |      | dB  |

| $f_{SW}$          | 调制频率         | $V_{\rm DD} = 3.0 \text{V to } 5.25 \text{V}$                 |     | 450 |      | kHz |

| η                 | 效率           | $P_0=1W, R_L=4\Omega, V_{DD}=3.6V$                            |     | 85  |      | %   |

| <b>V</b> IH       | 逻辑控制端<br>高电平 |                                                               | 1.4 |     |      | V   |

| <b>V</b> IL       | 逻辑控制端<br>低电平 |                                                               |     |     | 0.4  | V   |

#### 超低EMI、无需滤波器、3W双声道D类音频功放

| P <sub>O</sub>      | 输出功率    | THD+N=1%,<br>f=1KHz, $R_L$ =3 $\Omega$                                  | 2.5 | W  |

|---------------------|---------|-------------------------------------------------------------------------|-----|----|

|                     |         | THD+N=1%,<br>f=1KHz, $R_L$ =4 $\Omega$                                  | 2.0 | W  |

|                     |         | THD+N=1%,<br>f=1KHz, $R_L$ =8 $\Omega$                                  | 1.2 | W  |

|                     |         | THD+N=10%,<br>f=1KHz, $R_L$ =3 $\Omega$                                 | 3.0 | W  |

|                     |         | THD+N=10%,<br>f=1KHz, $R_L$ =4 $\Omega$                                 | 2.5 | W  |

|                     |         | THD+N=10%,<br>f=1KHz, $R_L$ =8 $\Omega$                                 | 1.5 | W  |

| THD+N               | 总失真度+噪声 | $A_{VD}$ =2, 20Hz $\leq$ f $\leq$ 20KHz $R_L$ =8 $\Omega$ , $P_0$ =0.5W | 0.2 | %  |

| Stereo<br>Isolation | 立体声分离度  | $RL=8\Omega$ , $Po=0.5W$                                                | -80 | dB |

| SNR                 | 信噪比     | $RL=8\Omega$ , $Po=0.5W$                                                | 90  | dB |

# 7 芯片管脚描述

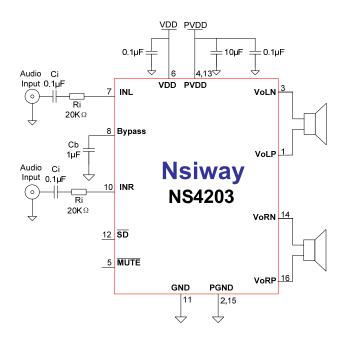

## 7.1 SOP16 封装管脚分配图

图2 SOP16 封装管脚分配图(top view)

# 7.2 引脚功能描述

表3 NS4203 管脚描述

| 符号     | 管脚号 | 描述             |

|--------|-----|----------------|

| VoLP   | 1   | 左声道输出正端        |

| PGND   | 2   | 功率地            |

| VoLN   | 3   | 左声道输出负端        |

| PVDD   | 4   | 功率电源输入         |

| /MUTE  | 5   | 待机控制,低电平有效(待机) |

| VDD    | 6   | 电源输入           |

| INL    | 7   | 左声道输入          |

| Bypass | 8   | 旁路电容           |

| NC     | 9   | 空脚             |

| INR    | 10  | 右声道输入          |

| GND    | 11  | 电源地            |

| /SD    | 12  | 关断控制,低电平有效(关断) |

| PVDD   | 13  | 功率电源输入         |

| VoRN   | 14  | 右声道输出负端        |

| PGND   | 15  | 功率地            |

| VoRP   | 16  | 右声道输出正端        |

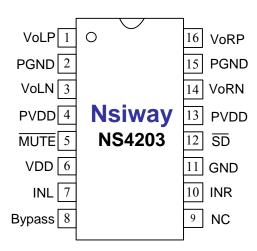

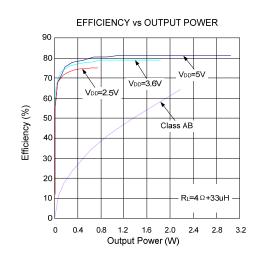

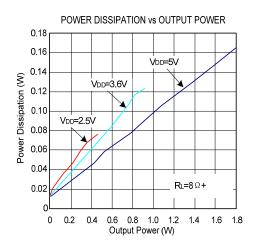

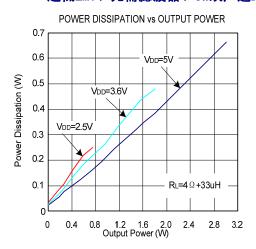

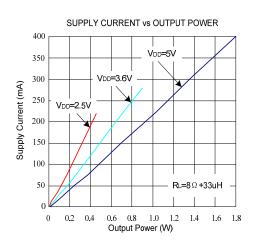

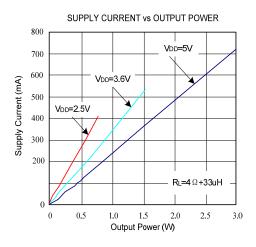

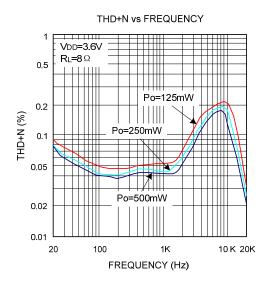

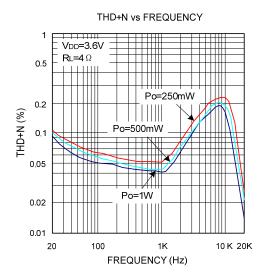

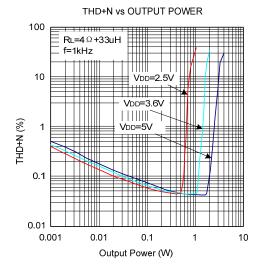

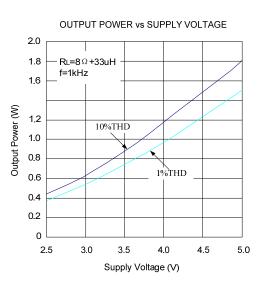

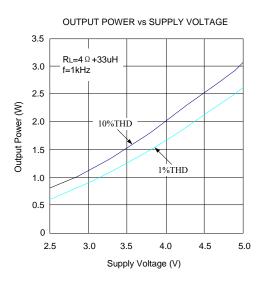

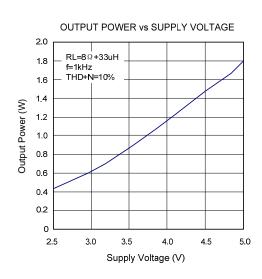

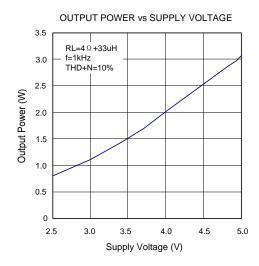

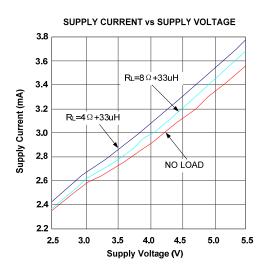

# 8 NS4203 典型参考特性

#### 超低EMI、无需滤波器、3W双声道D类音频功放

0.01

0.001

0.01

#### 超低EMI、无需滤波器、3W双声道D类音频功放

# 100 RL=8 Ω +33uH f=1kHz 10 VDD=2.5V VDD=3.6V VDD=5V 0.1

0.1

Output Power (W)

10

1

THD+N vs OUTPUT POWER

#### 超低EMI、无需滤波器、3W双声道D类音频功放

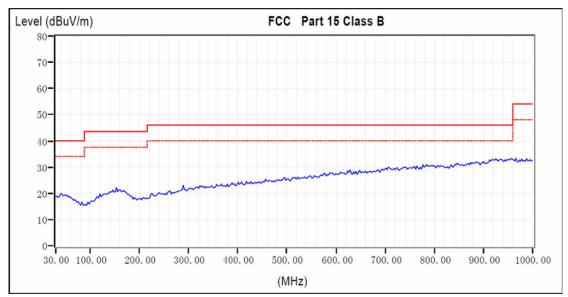

# 9 NS4203 应用说明

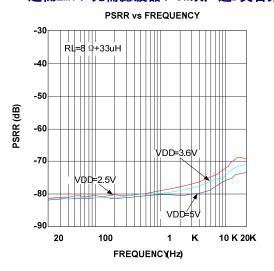

#### 9.1 芯片基本结构描述

NS4203 是双声道 D 类音频功率放大器。芯片内部每个通道集成了反馈电阻,放大器的增益可以在外围通过输入电阻设置。其原理框图如下:

图3 NS4203 原理框图

#### 9.2 NS4203 工作模式

NS4203的工作模式通过管脚/SD和/MUTE设置,如下表

表4 NS4203 工作模式设置

| /SD | /MUTE | 工作模式  |

|-----|-------|-------|

| 高   | 高     | 正常工作  |

| 高   | 低     | 待机状态  |

| 低   | 低/高   | 低功耗关断 |

#### 增益设置

芯片内部调制级的增益为 3,每个通道总增益为 Av=240k/Ri。Ri 为外接输入电阻。

#### 输入电容 Ci 和输入电阻 Ri 选择

输入电容和输入电阻构成高通滤波器,截止频率为  $f_{-3dB} = \frac{1}{2\pi R_{IN}C_{I}}$ 。过大的输入电容,增加成

本、增加面积,这对于成本、面积紧张的应用来讲,非常不利。显然,确定使用多大的电容来完成耦合很重要。实际上,在很多应用中,扬声器(Speaker)不能够再现低于 100Hz-150Hz 的低频语音,因此采用大的电容并不能够改善系统的性能。除了考虑系统的性能,开关/切换噪声的抑制性能受电容的影响,如果耦合电容大,则反馈网络的延迟大,导致 pop 噪声出现,因此,小的耦合电容可以减少该噪声。

#### 旁路电容 Cb 选择

Cb 决定 NS4203 静态工作点的稳定性,所以当开启有爆裂的输入信号时它的值非常关键。Cb 越大,芯片的输出倾斜到静态直流电压(即 VDD/2) 越慢,则开启的爆裂声越小。Cb 取 1uF 可得到一个"滴答声"和"爆裂声"都较小的关断功能。

#### 电源滤波电容选择

在放大器的应用中,电源的旁路设计很重要,特别是对应用方案的噪声性能及电源电压抑制性能。设计中要求滤波电容尽量靠近芯片电源脚。典型的电容为100uF的电解电容并上0.1uF的陶瓷电容。

#### 低功耗关断功能

当/SD 管脚电平为低时,芯片处于关断低功耗状态。实际应用中建议 SD 管脚接下拉电阻。这样保证与/SD 管脚相连悬空或者高阻时芯片处于关断状态。

#### 待机状态控制功能

当/SD 管脚电平为高,/MUTE 管脚电平为低时。芯片进入待机状态。实际应用中建议/MUTE 管脚接下拉电阻。这样保证与/MUTE 管脚相连悬空或者高阻时芯片处于待机状态。

#### 9.3 上电,掉电噪声抑制

NS4203 内置上电,掉电噪声抑制电路,有效地消除了系统在上电、下电、唤醒和关断操作时可能出现的瞬态噪声。

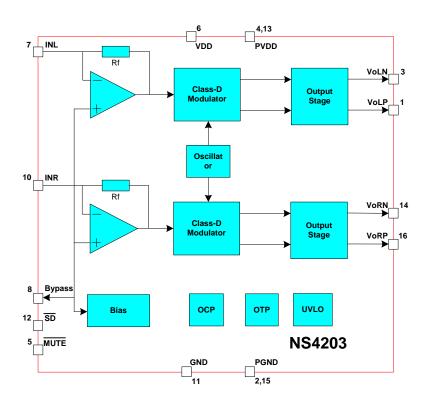

#### 9.4 EMI增强技术

NS4203 内置 EMI 增强技术。 采用先进的技术,在全带宽范围内极大地降低了 EMI 干扰,最大限度地减少对其他部件的影响。如图 6 所示。

图4 EMI测试频谱图

#### 9.5 效率

NS4203 利用扩展频谱技术充分优化全新 D 类放大器的电路设计,以提高效率。最高可达 85%的效率 更加适合于手机及其他便携式音频产品。

#### 9.6 保护电路

当芯片发生输出引脚与电源或地短路,或者输出之间的短路故障时,过流保护电路会关断芯片以防止芯片被损坏。短路故障消除后,NS4203自动恢复工作。当芯片温度过高时,芯片也会被关断。温度下降后,NS4203继续正常工作。当电源电压过低时,芯片同样会被关断,电源电压恢复后,芯片会再次启动。

## 10 NS4203 应用注意事项

#### D 类音频功放 EMI 干扰来源

D 类音频功放的 EMI 干扰主要来源于两个地方。一个是电源线上电流的跳动;另外一个是输出端脉冲信号的边沿。EMI 主要通过 PCB 的走线、通孔和扬声器的连线向外辐射,干扰其他的部件。

#### NS4203 超低 EMI

便携音频设备电池的寿命和音频功放的效率直接相关。D类音频功放的效率对于延长电池的使用时间是无容置疑。但是对有收音模块的设备来讲,传统 D类音频功放的 EMI 干扰直接限制了 D类功放的使用,令许多设计工程师头痛。NS4203 采用先进的 EMI 增强技术,非常有效降低了 EMI 干扰。

#### NS4203 应用设计参考

要充分发挥 D 类功放的性能。应用时从以下几个方面可以最大限度降低 D 类音频功放的 EMI 干扰:

- 1. 功放输出到喇叭的走线,连线尽量短,尽量宽,而且输出布线,连线尽可能远离敏感信号线和电路。

- 2. 功放电源脚的去耦电容尽可能靠近芯片引脚。电源线,地线最好采用星形接法。

- 3. 由于空间限制等原因 EMI 干扰较严重时在输出端加磁珠和电容可以有效抑制 EMI 干扰。使用时磁珠和电容尽可能靠近芯片引脚。以下是 NS4203 加了磁珠之后的应用设计参考电路:

Nsiway 13

图5 NS4203 加磁珠应用电路

# 11 芯片的封装

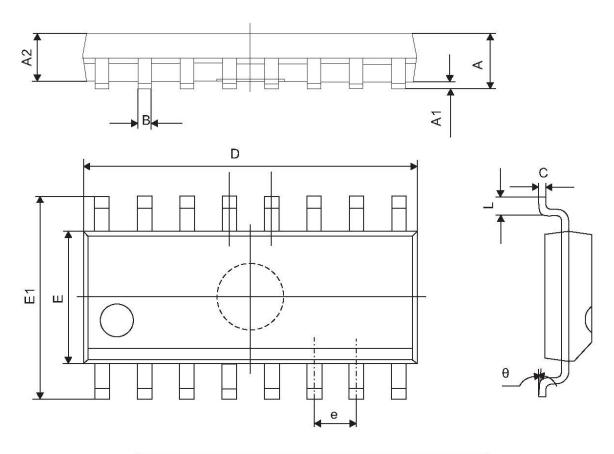

# 11.1 SOP16 封装尺寸图

| Symbol | Dimensions Millimeters |        |  |  |

|--------|------------------------|--------|--|--|

|        | Min                    | Max    |  |  |

| Α      | 1.350                  | 1.750  |  |  |

| A1     | 0.100                  | 0.250  |  |  |

| A2     | 1.350                  | 1.550  |  |  |

| В      | 0.330                  | 0.510  |  |  |

| С      | 0.190                  | 0.250  |  |  |

| D      | 9.800                  | 10.000 |  |  |

| Е      | 3.800                  | 4.000  |  |  |

| E1     | 5.800                  | 6.300  |  |  |

| е      | 1.270                  | (TYP)  |  |  |

| L      | 0.400                  | 1.270  |  |  |

| θ      | 0°                     | 8°     |  |  |

图6 SOP16 封装尺寸图

声明:深圳市纳芯威科技有限公司保留在任何时间,并且没有通知的情况下修改产品资料和产品规格的权利,本手册的解释权归深圳市纳芯威科技有限公司所有,并负责最终解释。