# 具可配置数字滤波器的 32 位过采样 ADC

## 特点

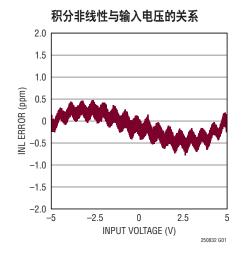

- ±0.5ppm INL (典型值)

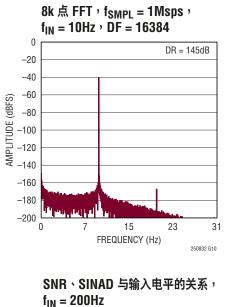

- 在 61sps 时具有 145dB 动态范围 (典型值)

- 在 4ksps 时具有 131dB 动态范围 (典型值)

- 保证 32 位,无漏失码

- 具同步功能的可配置数字滤波器

- 放宽的抗混迭滤波器要求

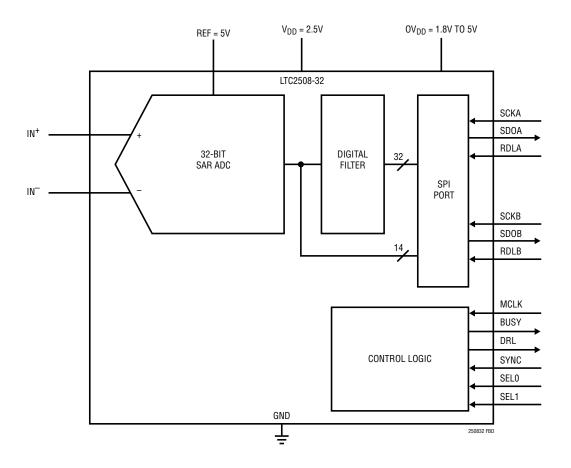

- 双输出 32 位 SAR ADC

- 32 位数字滤波低噪声输出

- 14 位差分 + 8 位共模 1Msps 无延迟输出

- 宽输入共模范围

- 保证工作至 85°C

- 1.8V 至 5V SPI 兼容型串行 I/O

- 低功耗: 24mW (在 1Msps)

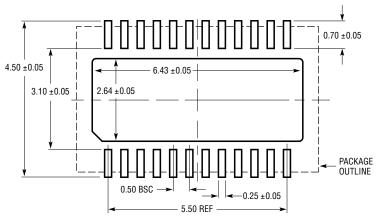

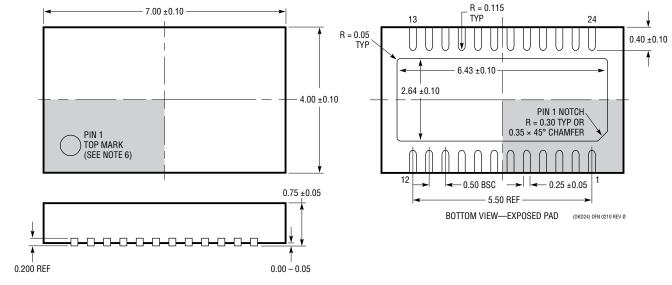

- 24 引脚 7mm x 4mm DFN 封装

## 应用

- 地震学

- 能源勘探

- 自动化测试设备 (ATE)

- 高准确度仪表

▲**ブ**、LT、LTC、LTM、Linear Technology 和 Linear 标识是凌力尔特公司的注册商标,SoftSpan 是凌力尔特公司的商标。所有其他商标均为其各自拥有者的产权。受包括第7705765、7961132、8319673、8576104、8810443、9054727、9231611 和 9331709 号美国专利的保护,并正待专利审议。

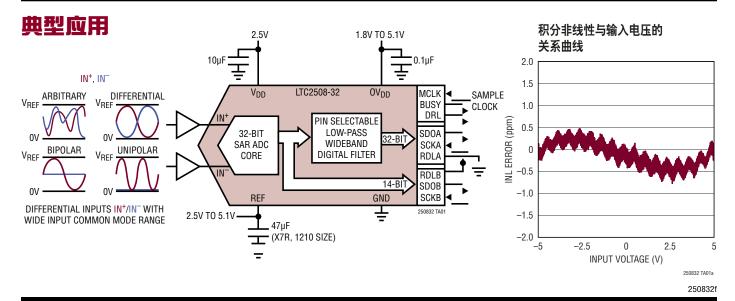

## 描述

LTC®2508-32 是一款低噪声、低功耗、高性能 32 位 ADC,其具有一个集成的可配置数字滤波器。LTC2508-32 采用单个 2.5V 工作电源,具有一个高达  $\pm V_{REF}$  的全差分输入范围,且  $V_{REF}$  的范围从 2.5V 至 5.1V。LTC2508-32 支持 OV 至  $V_{REF}$  的宽共模范围,从而简化了模拟信号调理要求。

LTC2508-32 同时提供两个输出代码:(1) 一个 32 位数字 滤波高精度低噪声代码;和(2) 一个 22 位无延迟复合代码。可配置数字滤波器通过对来自 SAR ADC 内核的数据流实施低通滤波和降频采样以降低测量噪声,产生了 32 位滤波输出代码。22 位复合代码由一个代表差分电压的 14 位代码和一个代表共模电压的 8 位代码组成。22 位复合代码可在每个转换周期中提供,并没有延迟周期。

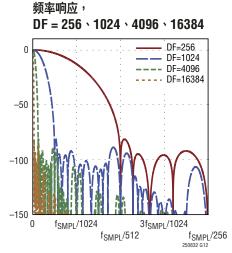

可通过引脚搭接方便地针对 4 种不同的降频转换因子配置数字滤波器。这些配置提供一个 131dB (在 3.9ksps) 和 145dB (在 61sps) 的动态范围。数字低通滤波器放宽了对于模拟抗混迭的要求。采用 SYNC 引脚可以很容易地实现多个 LTC2508-32 器件的同步。

## 绝对最大额定值

### (注1、2)

| 电源电压 (V <sub>DD</sub> ) 2.8 <sup>3</sup>             | V  |

|------------------------------------------------------|----|

| 电源电压 (OV <sub>DD</sub> ) 69                          | V  |

| 基准输入 (REF) 6 <sup>v</sup>                            | V  |

| 模拟输入电压 (注 3)                                         |    |

| IN+, IN(GND-0.3V) 至 (REF+0.3V                        | () |

| 数字输入电压 (注 3) (GND - 0.3V) 至 (OV <sub>DD</sub> + 0.3V | () |

| 数字输出电压 (注 3) (GND - 0.3V) 至 (OV <sub>DD</sub> + 0.3V | () |

| 功率耗散 500mV                                           | ۷  |

| 工作温度范围                                               |    |

| LTC2508C-32 0°C 至 70°C                               | C  |

| LTC2508I-32                                          | C  |

| 贮存温度范围65°C 至 150°C                                   | C  |

|                                                      |    |

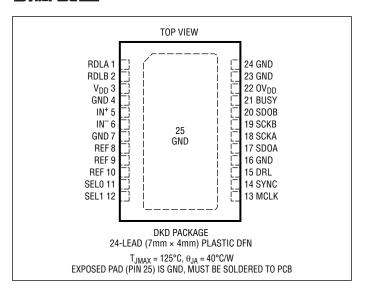

## 引脚配置

## 订购信息 http://www.linear.com.cn/product/LTC2508-32#orderinfo

| 无铅涂层               | 卷带                   | 器件标记*  | 封装描述                     | 温度范围         |

|--------------------|----------------------|--------|--------------------------|--------------|

| LTC2508CDKD-32#PBF | LTC2508CDKD-32#TRPBF | 250832 | 24 引脚 (7mm x 4mm) 塑料 DFN | 0°C 至 70°C   |

| LTC2508IDKD-32#PBF | LTC2508IDKD-32#TRPBF | 250832 | 24 引脚 (7mm x 4mm) 塑料 DFN | -40°C 至 85°C |

对于规定工作温度范围更宽的器件,请咨询凌力尔特公司。 \*温度等级请见集装箱上的标识。

如需了解更多有关无铅器件标记的信息,请登录:http://www.linear.com.cn/leadfree/

如需了解更多有关卷带规格的信息,请登录:http://www.linear.com.cn/tapeandreel/。有些封装可通过指定的销售渠道以 500 片的卷盘形式供货 (具有 #TRMPBF 后缀)。

## 电气特性 凡标注 ● 表示该指标适合整个工作温度范围,否则仅指 T<sub>A</sub> = 25°C。(注 4)

| 符号                    | 参数           | 条件                                                                                                               |   | 最小值               | 典型值 | 最大值       | 单位 |

|-----------------------|--------------|------------------------------------------------------------------------------------------------------------------|---|-------------------|-----|-----------|----|

| V <sub>IN</sub> +     | 绝对输入范围 (IN+) | (注 5)                                                                                                            | • | 0                 |     | $V_{REF}$ | V  |

| $V_{IN}^-$            | 绝对输入范围 (IN-) | (注 5)                                                                                                            | • | 0                 |     | $V_{REF}$ | V  |

| $V_{IN}^+ - V_{IN}^-$ | 输入差分电压范围     | $V_{IN} = V_{IN}^+ - V_{IN}^-$                                                                                   | • | -V <sub>REF</sub> |     | $V_{REF}$ | V  |

| V <sub>CM</sub>       | 共模输入范围       |                                                                                                                  | • | 0                 |     | $V_{REF}$ | V  |

| I <sub>IN</sub>       | 模拟输入漏电流      |                                                                                                                  |   |                   | 10  |           | nA |

| C <sub>IN</sub>       | 模拟输入电容       | 采样模式                                                                                                             |   |                   | 45  |           | pF |

|                       |              | 保持模式                                                                                                             |   |                   | 5   |           | pF |

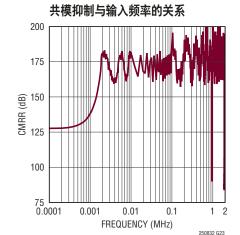

| CMRR                  | 输入共模抑制比      | 滤波输出<br>V <sub>IN</sub> <sup>+</sup> = V <sub>IN</sub> <sup>-</sup> = 4.5V <sub>P-P</sub> <sup>,</sup> 200Hz 正弦波 |   |                   | 128 | ·         | dB |

LINEAR TECHNOLOGY

## 滤波输出 (SDOA) 的转换器特性 凡标注 ● 表示该指标适合整个工作温度范围, 否则仅指 TA = 25°C。(注 4)

| 符号  | 参数      | 条件                                   |      |   | 最小值  | 典型值                            | 最大值   | 单位                       |

|-----|---------|--------------------------------------|------|---|------|--------------------------------|-------|--------------------------|

|     | 分辨率     |                                      |      | • | 32   |                                |       | 位                        |

|     | 无漏失码    |                                      |      | • | 32   |                                |       | 位                        |

| DF  | 降频采样因子  |                                      |      | • | 256  |                                | 16384 |                          |

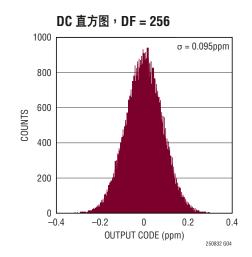

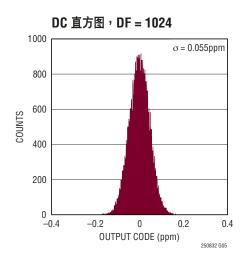

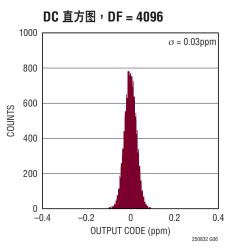

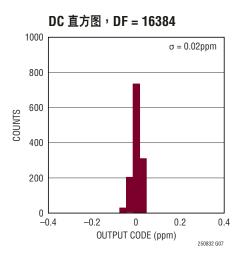

|     | 转换噪声    | DF = 2<br>DF = 2<br>DF = 4<br>DF = 3 | 1096 |   |      | 0.095<br>0.055<br>0.03<br>0.02 |       | ppm<br>ppm<br>ppm<br>ppm |

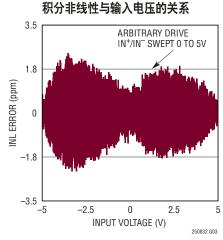

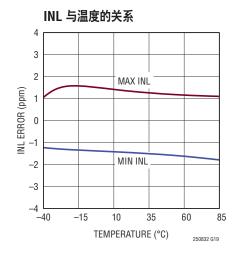

| INL | 积分线性误差  | (注 7)                                |      | • | -3.5 | 0.5                            | 3.5   | ppm                      |

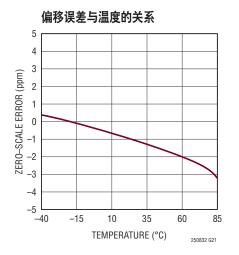

| ZSE | 零标度误差   | (注 9)                                |      | • | -13  | 0                              | 13    | ppm                      |

|     | 零标度误差漂移 |                                      |      |   |      | ±14                            |       | ppb/°C                   |

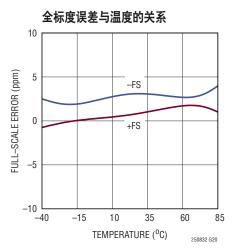

| FSE | 全标度误差   | (注 9)                                |      | • | -100 | ±10                            | 100   | ppm                      |

|     | 全标度误差漂移 |                                      |      |   |      | ±0.05                          |       | ppm/°C                   |

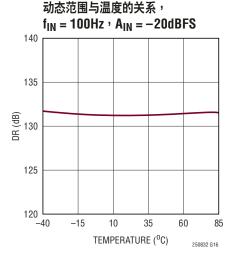

# 滤波输出 (SDOA) 的动态准确度 凡标注 ● 表示该指标适合整个工作温度范围,否则仅指 T<sub>A</sub> = 25°C 和 A<sub>IN</sub> = -20dBFS。(注 4、10)

| 符号   | 参数        | 条件                                                           |   | 最小值 | 典型值  | 最大值  | 单位                |

|------|-----------|--------------------------------------------------------------|---|-----|------|------|-------------------|

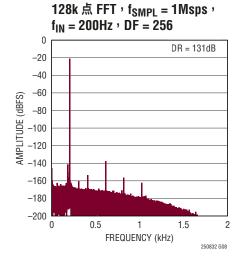

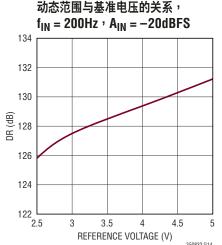

| DR   | 动态范围      | V <sub>REF</sub> = 5V <sup>,</sup> DF = 256                  | • | 125 | 131  |      | dB                |

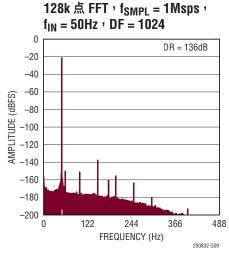

|      |           | $ IN^{+} = IN^{-} = V_{CM}^{-}, V_{REF} = 5V^{-}, DF = 1024$ |   |     | 136  |      | dB                |

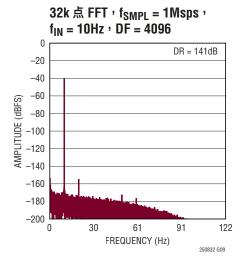

|      |           | $IN^{+} = IN^{-} = V_{CM}$ , $V_{REF} = 5V$ , $DF = 4096$    |   |     | 141  |      | dB                |

|      |           | $IN^{+} = IN^{-} = V_{CM}$ , $V_{REF} = 5V$ , $DF = 16384$   |   |     | 145  |      | dB                |

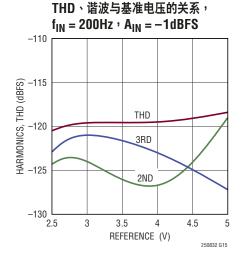

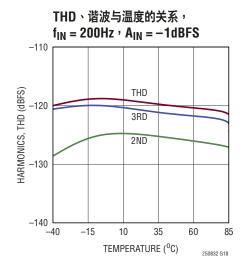

| THD  | 总谐波失真     | $f_{IN} = 200Hz$ , $V_{REF} = 2.5V$ , $DF = 256$             |   |     | -118 |      | dB                |

|      |           | $f_{IN} = 200Hz$ , $V_{REF} = 5V$ , $DF = 256$               | • |     | -118 | -108 | dB                |

| SFDR | 无杂散动态范围   | f <sub>IN</sub> = 200Hz , V <sub>RFF</sub> = 2.5V , DF = 256 |   |     | 118  |      | dB                |

|      |           | f <sub>IN</sub> = 200Hz , V <sub>REF</sub> = 5V , DF = 256   | • | 108 | 118  |      | dB                |

|      | -3dB 输入带宽 |                                                              |   |     | 34   |      | MHz               |

|      | 孔径延迟      |                                                              |   |     | 500  |      | ps                |

|      | 孔径抖动      |                                                              |   |     | 4    |      | ps <sub>RMS</sub> |

|      | 瞬态响应      | 全标度阶跃                                                        |   |     | 125  |      | ns                |

# **无延迟输出 (SDOB) 的转换器特性** 凡标注 ● 表示该指标适合整个工作温度范围,否则仅指 T<sub>A</sub> = 25°C。(注 4)

| 符号  | 参数                 | 条件                            |   | 最小值     | 典型值          | 最大值 | 单位                 |

|-----|--------------------|-------------------------------|---|---------|--------------|-----|--------------------|

|     | 分辨率:<br>差分<br>共模   | 差分                          ● |   | 14<br>8 |              |     | 位<br>位             |

|     | 无漏失码:<br>差分<br>共模  |                               | • | 14<br>8 |              |     | 位<br>位             |

|     | 转换噪声<br>差分<br>共模   | (注 6)                         |   |         | 1<br>1       |     | LSB <sub>RMS</sub> |

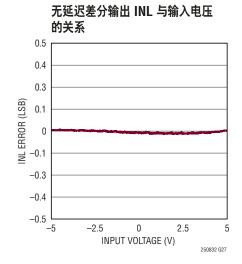

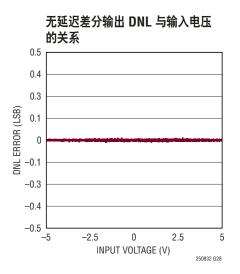

| INL | 积分线性误差<br>差分<br>共模 | (注 7)                         |   |         | ±0.1<br>±0.1 |     | LSB<br>LSB         |

| DNL | 差分线性误差<br>差分<br>共模 |                               |   |         | ±0.1<br>±0.1 |     | LSB<br>LSB         |

| ZSE | 零标度误差<br>差分<br>共模  |                               |   |         | ±1<br>±1     |     | LSB<br>LSB         |

| FSE | 全标度误差<br>差分<br>共模  |                               |   |         | ±1<br>±1     |     | LSB<br>LSB         |

## 基准输入 凡标注 ● 表示该指标适合整个工作温度范围,否则仅指 T<sub>A</sub> = 25°C。(注 4、9)

| 符号               | 参数     | 条件     |   | 最小值 | 典型值 | 最大值 | 单位 |

|------------------|--------|--------|---|-----|-----|-----|----|

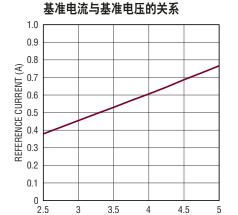

| $V_{REF}$        | 基准电压   | (注 5)  | • | 2.5 |     | 5.1 | V  |

| I <sub>REF</sub> | 基准输入电流 | (注 11) | • |     | 0.7 | 1   | mA |

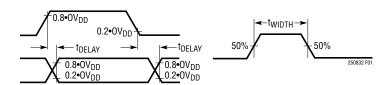

## 数字输入和数字输出 凡标注 ● 表示该指标适合整个工作温度范围,否则仅指 T<sub>A</sub> = 25°C。(注 4)

| 符号                  | 参数       | 条件                                       |   | 最小值                    | 典型值 | 最大值                    | 单位 |

|---------------------|----------|------------------------------------------|---|------------------------|-----|------------------------|----|

| V <sub>IH</sub>     | 高电平输入电压  |                                          | • | 0.8 • OV <sub>DD</sub> |     |                        | V  |

| V <sub>IL</sub>     | 低电平输入电压  |                                          | • |                        |     | 0.2 • OV <sub>DD</sub> | V  |

| I <sub>IN</sub>     | 数字输入电流   | V <sub>IN</sub> = 0V 至 0V <sub>DD</sub>  | • | -10                    |     | 10                     | μA |

| C <sub>IN</sub>     | 数字输入电容   |                                          |   |                        | 5   |                        | pF |

| V <sub>OH</sub>     | 高电平输出电压  | $I_0 = -500 \mu A$                       | • | $0V_{DD} - 0.2$        |     |                        | V  |

| $V_{OL}$            | 低电平输出电压  | Ι <sub>0</sub> = 500μΑ                   | • |                        |     | 0.2                    | V  |

| I <sub>OZ</sub>     | 高阻抗输出漏电流 | V <sub>OUT</sub> = 0V 至 OV <sub>DD</sub> | • | -10                    |     | 10                     | μA |

| I <sub>SOURCE</sub> | 输出供应电流   | V <sub>OUT</sub> = 0V                    |   |                        | -10 |                        | mA |

| I <sub>SINK</sub>   | 输出吸收电流   | $V_{OUT} = OV_{DD}$                      |   |                        | 10  |                        | mA |

TECHNOLOGY TECHNOLOGY

## 电源要求 凡标注 ● 表示该指标适合整个工作温度范围,否则仅指 T<sub>A</sub> = 25°C。(注 4)

| 符号                                                       | 参数                   | 条件                                                                                                                    |   | 最小值   | 典型值           | 最大值         | 单位             |

|----------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------|---|-------|---------------|-------------|----------------|

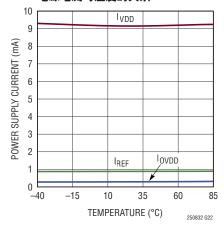

| $V_{DD}$                                                 | 电源电压                 |                                                                                                                       | • | 2.375 | 2.5           | 2.625       | V              |

| OV <sub>DD</sub>                                         | 电源电压                 |                                                                                                                       | • | 1.71  |               | 5.25        | V              |

| I <sub>VDD</sub><br>I <sub>OVDD</sub><br>I <sub>PD</sub> | 电源电流<br>电源电流<br>断电模式 | 1Msps 采样速率<br>1Msps 采样速率 (C <sub>L</sub> = 20pF)<br>转换操作完成 (I <sub>VDD</sub> + I <sub>OVDD</sub> + I <sub>REF</sub> ) | • |       | 9.5<br>1<br>6 | 13<br>350   | mA<br>mA<br>μA |

| P <sub>D</sub>                                           | 功耗<br>断电模式           | 1Msps 采样速率 (I <sub>VDD</sub> )<br>转换操作完成 (I <sub>VDD</sub> + I <sub>OVDD</sub> + I <sub>REF</sub> )                   |   |       | 24<br>15      | 32.5<br>875 | mW<br>μW       |

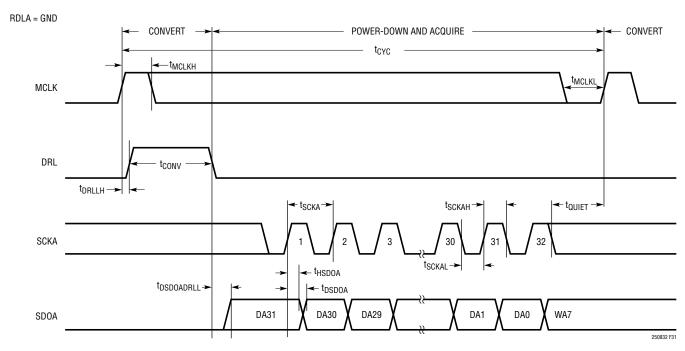

## ADC 定时特性 凡标注 ● 表示该指标适合整个工作温度范围,否则仅指 T<sub>A</sub> = 25°C。(注 4)

| 符号                                          | 参数                       | 条件                                                                                  |   | 最小值  | 典型值 | 最大值        | 单位       |

|---------------------------------------------|--------------------------|-------------------------------------------------------------------------------------|---|------|-----|------------|----------|

| f <sub>SMPL</sub>                           | 最大采样频率                   |                                                                                     | • |      |     | 1          | Msps     |

| f <sub>DRA</sub>                            | 在 SDOA 上的输出数据速率          |                                                                                     | • |      |     | 3.9        | ksps     |

| f <sub>DRB</sub>                            | 在 SDOB 上的输出数据速率          |                                                                                     | • |      |     | 1          | Msps     |

| t <sub>CONV</sub>                           | 转换时间                     |                                                                                     | • | 578  |     | 652        | ns       |

| $\overline{t_{ACQ}}$                        | 采集时间                     | t <sub>ACQ</sub> = t <sub>CYC</sub> - t <sub>CONV</sub> - t <sub>BUSYLH</sub> (注 8) | • | 335  |     |            | ns       |

| t <sub>CYC</sub>                            | 转换间隔时间                   |                                                                                     | • | 1000 |     |            | ns       |

| t <sub>MCLKH</sub>                          | MCLK 高电平时间               |                                                                                     | • | 20   |     |            | ns       |

| t <sub>MCLKL</sub>                          | MCLK 的最小低电平时间            | (注 12)                                                                              | • | 20   |     |            | ns       |

| t <sub>BUSYLH</sub>                         | MCLK↑ 至 BUSY↑ 延迟         | C <sub>L</sub> = 20pF                                                               | • |      |     | 13         | ns       |

| t <sub>DRLLH</sub>                          | MCLK↑至 DRL↑延迟            | C <sub>L</sub> = 20pF                                                               | • |      |     | 18         | ns       |

| t <sub>QUIET</sub>                          | SCKA、SCKB 静态时间 (自 MCLK↑) | (注 8)                                                                               | • | 10   |     |            | ns       |

| t <sub>SCKA</sub>                           | SCKA 周期                  | (注 12、13)                                                                           | • | 10   |     |            | ns       |

| t <sub>SCKAH</sub>                          | SCKA 高电平时间               |                                                                                     | • | 4    |     |            | ns       |

| t <sub>SCKAL</sub>                          | SCKA 低电平时间               |                                                                                     | • | 4    |     |            | ns       |

| t <sub>DSDOA</sub>                          | SDOA 数据有效延迟 (自 SCKA↑)    | C <sub>L</sub> = 20pF , OV <sub>DD</sub> = 5.25V                                    | • |      |     | 8.5        | ns       |

|                                             |                          | $C_L = 20pF \cdot OV_{DD} = 2.5V$<br>$C_L = 20pF \cdot OV_{DD} = 1.71V$             | • |      |     | 8.5<br>9.5 | ns<br>ns |

| t <sub>HSDOA</sub>                          | SDOA 数据保持有效延迟 (自 SCKA↑)  | C <sub>L</sub> = 20pF (注 8)                                                         |   | 1    |     | 9.0        | ns       |

|                                             | SDOA 数据有效延迟 (自 DRL↓)     | C <sub>1</sub> = 20pF (注 8)                                                         |   | '    |     | 5          | ns       |

| t <sub>DSDOADRLL</sub><br>t <sub>ENAA</sub> | RDLA』之后的总线启用时间           | (注 12)                                                                              |   |      |     | 16         | ns       |

|                                             | RDLA↑之后的总线释放时间           | (注 12)                                                                              |   |      |     | 13         | ns       |

| tour                                        | SCKB 周期                  | (注 12、13)                                                                           |   | 10   |     | 10         | ns       |

| tsckb                                       | SCKB 高电平时间               | (/12 10)                                                                            |   | 4    |     |            | ns       |

| t <sub>SCKBH</sub>                          | SCKB 低电平时间               |                                                                                     |   | 4    |     |            |          |

| t <sub>SCKBL</sub>                          |                          | 0 00 5 00 5 050                                                                     | _ | 4    |     | 0.5        | ns       |

| t <sub>DSDOB</sub>                          | SDOB 数据有效延迟 (自 SCKB↑)    | $C_L = 20pF \cdot 0V_{DD} = 5.25V$<br>$C_L = 20pF \cdot 0V_{DD} = 2.5V$             |   |      |     | 8.5<br>8.5 | ns<br>ns |

|                                             |                          | $C_L = 20pF \cdot 0V_{DD} = 2.3V$<br>$C_L = 20pF \cdot 0V_{DD} = 1.71V$             |   |      |     | 9.5        | ns       |

| t <sub>HSDOB</sub>                          | SDOB 数据保持有效延迟 (自 SCKB↑)  | C <sub>L</sub> = 20pF (注 8)                                                         | • | 1    |     |            | ns       |

## ADC 定时特性 凡标注 ● 表示该指标适合整个工作温度范围, 否则仅指 T<sub>A</sub> = 25°C。(注 4)

| 符号                      | 参数                    | 条件                          |   | 最小值 | 典型值 | 最大值 | 单位 |

|-------------------------|-----------------------|-----------------------------|---|-----|-----|-----|----|

| t <sub>DSDOBBUSYL</sub> | SDOB 数据有效延迟 (自 BUSY↓) | C <sub>L</sub> = 20pF (注 8) | • |     |     | 5   | ns |

| t <sub>ENB</sub>        | RDLB↓之后的总线启用时间        | (注 12)                      | • |     |     | 16  | ns |

| t <sub>DISB</sub>       | RDLB↑之后的总线释放时间        | (注 12)                      | • |     |     | 13  | ns |

**注1**: 高于"绝对最大额定值"部分所列数值的应力有可能对器件造成永久性的损害。在任何绝对最大额定值条件下暴露的时间过长都有可能影响器件的可靠性和使用寿命。

注 2: 所有的电压值均以地电位基准。

注 3: 当把这些引脚电压拉至低于地电位或者高于 REF 或  $OV_{DD}$  时,它们将被内部二极管所箝位。在低于地电位或者高于 REF 或  $OV_{DD}$  的情况下,本产品能处理高达 100mA 的输入电流,且不会发生闭锁。

注  $4: V_{DD} = 2.5V, OV_{DD} = 2.5V$ ,REF = 5V, $V_{CM} = 2.5V$ , $f_{SMPL} = 1MHz$ ,DF = 256。

注 5: 推荐的工作条件。

注 6:转换噪声被定义为 IN+和 IN-短接时 ADC 的噪声电平。

注 7:积分非线性被定义为一个代码相对一根穿过转移函数曲线实际端点的直线的偏离程度。该偏离是以量化频带的中心为起点进行测量的。

注8:由设计提供保证,未经测试。

注 10: 所有以 dB 为单位的规格均参考于一个全标度  $\pm 5V$  输入和一个 5V 基准电压。

注 11: f<sub>SMPI</sub> = 1MHz, I<sub>RFF</sub> 随采样速率成比例地改变。

注 12:在  $OV_{DD} = 1.71V \cdot OV_{DD} = 2.5V$  和  $OV_{DD} = 5.25V$  的条件下对参数 提供测试与保证。

注 13:10ns (最大值) 的 t<sub>SCKA</sub>、t<sub>SCKB</sub> 可提供一个用于上升沿捕获的高达 100MHz 的移位时钟频率。

图 1:用于时序规格的电压电平

典型II 指行 T<sub>A</sub> = 25°C , V<sub>DD</sub> = 2.5V , OV<sub>DD</sub> = 2.5V , V<sub>CM</sub> = 2.5V , REF = 5V , f<sub>SMPL</sub> = 1Msps , DF = 256 , 滤波输出,除非特别注明。

LINEAR

典型性能特征 T<sub>A</sub> = 25°C, V<sub>DD</sub> = 2.5V, OV<sub>DD</sub> = 2.5V, V<sub>CM</sub> = 2.5V, REF = 5V, f<sub>SMPL</sub> = 1Msps, DF = 256,

滤波输出,除非特别注明。

动态范围、转换噪声与 DF 的关系 0.10 150 0.08 145 0.08 TRANSITION NOISE (ppm) DYNAMIC RANGE (dB) 140 135 130 0.02 125 <del>-</del> 256 16384 1024 4096 DOWN SAMPLING FACTOR (DF)

f<sub>IN</sub> = 200Hz

140

135

SNR

(S49)

125

110

-40

-30

-20

-10

(G99)

125

INPUT LEVEL (dB)

##

滤波输出,除非特别注明。

#### 电源电流与温度的关系

REFERENCE VOLTAGE (V)

250832 G24

**典型性指征** T<sub>A</sub> = 25°C , V<sub>DD</sub> = 2.5V , OV<sub>DD</sub> = 2.5V , V<sub>CM</sub> = 2.5V , REF = 5V , f<sub>SMPL</sub> = 1Msps , DF = 256 , 滤波输出,除非特别注明。

250832 G26

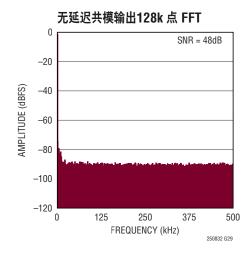

无延迟差分输出128k 点 FFT SNR = 86dB -20 -40 AMPLITUDE (dBFS) -60 -80 -100 -120 -140 -160 125 250 375 500 FREQUENCY (kHz)

## 引脚功能

RDLA (引脚 1):读低输入 A (滤波输出)。当 RDLA 为低电平时,串行数据输出 A (SDOA) 引脚被使能。当 RDLA 为高电平时,SDOA 引脚处于一种高阻抗状态。逻辑电平由 OV<sub>DD</sub> 决定。

RDLB (引脚 2): 读低输入 B (无延迟输出)。当 RDLB 为低电平时,串行数据输出 B (SDOB) 引脚被使能。当 RDLB 为高电平时,SDOB 引脚处于一种高阻抗状态。逻辑电平由  $OV_{DD}$  决定。

**V<sub>DD</sub> (引脚 3)**: 2.5V 电源。V<sub>DD</sub> 的范围为 2.375V 至 2.625V。采用一个 10μF 陶瓷电容器把 V<sub>DD</sub> 旁路至 GND。

GND (引脚 4、7、16、23、24):地。

IN+(引脚 5):正模拟输入。

IN-(引脚 6):负模拟输入。

**REF (引脚 8、9、10)**: 基准输入。REF 的范围为 2.5V 至 5.1V。该引脚参考于 GND 引脚,并应采用一个  $47\mu$ F 陶瓷电容器 (X7R,尺寸为 1210,额定电压为 10V) 紧密去耦至此引脚。

**SEL0、SEL1 (引脚 11、12)**:降频采样因子选择输入 0,降频采样因子选择输入 1。该引脚负责选择数字滤波器的降频采样因子。分别针对 00、01、10 和 11 的 [SEL0 SEL1]组合选择 256、1024、4096 和 16384 的降频采样因子。逻辑电平由 OV<sub>DD</sub> 决定。

MCLK (引脚 13): 主时钟输入。该输入端上的一个上升沿用于给器件上电并启动一个新的转换。逻辑电平由 OV<sub>DD</sub> 决定。

**SYNC (引脚 14)**:同步输入。该输入端上的一个脉冲用于实现数字滤波器相位的同步。逻辑电平由 OV<sub>DD</sub> 决定。

DRL (引脚 15):数据就绪低输出。该引脚上的一个下降沿表示在 SDOA 之输出寄存器中可提供一个新的滤波输出代码。逻辑电平由 OV<sub>DD</sub> 决定。

**SDOA (引脚 17)**:串行数据输出 A (滤波输出)。滤波输出代码在 SCKA 的每个上升沿在该引脚上输出 (MSB 最先输出)。输出数据为二进制补码格式。逻辑电平由 OV<sub>DD</sub> 决定。

SCKA (引脚 18): 串行数据时钟输入 A (滤波输出)。当 SDOA 被使能时, 滤波输出代码在该时钟的上升沿移出 (MSB 最先移出)。逻辑电平由 OV<sub>DD</sub> 决定。

**SCKB (引脚 19)**:串行数据时钟输入 B (无延迟输出)。当 SDOB 被使能时,无延迟输出代码在该时钟的上升沿移出 (MSB 最先移出)。逻辑电平由 OV<sub>DD</sub> 决定。

**SDOB (引脚 20)**: 串行数据输出 B (无延迟输出)。22 位无延迟复合输出代码在 SCKB 的每个上升沿在该引脚上输出 (MSB 最先输出)。输出数据为二进制补码格式。逻辑电平由 OV<sub>DD</sub> 决定。

BUSY (引脚 21): BUSY 指示器。该引脚在一个新转换的始端变至高电平,并在转换操作完成时返回低电平。逻辑电平由 OV<sub>DD</sub> 决定。

$OV_{DD}$  (引脚 22): I/O 接口数字电源。 $OV_{DD}$  的范围为 1.71V 至 5.25V。该电源一般被设定为与主机接口相同的电源  $(1.8V \cdot 2.5V \cdot 3.3V$  或 5V)。通过一个  $0.1\mu$ F 电容器把  $OV_{DD}$  旁路至靠近该引脚的 GND (引脚 23)。

GND (裸露衬垫引脚 25):地。裸露衬垫必须直接焊接至接地平面。

## 功能方框图

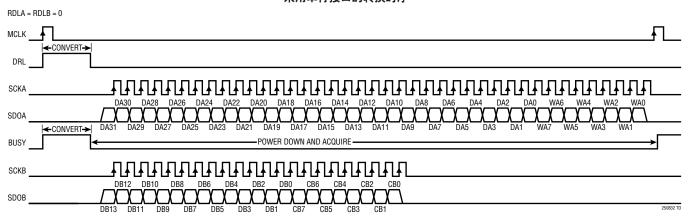

## 时序图

#### 采用串行接口的转换时序

## 工作原理

#### 概述

LTC®2508-32 是一款低噪声、低功耗、高性能 32 位 ADC,其具有一个集成的可配置数字滤波器。LTC2508-32 采用单个 2.5V 工作电源,具有高达  $\pm V_{REF}$  的全差分输入范围,且  $V_{REF}$  的范围从 2.5V 至 5.1V。LTC2508-32 支持 0V 至  $V_{REF}$  的宽共模范围,从而简化了模拟信号调理要求。

LTC2508-32 同时提供两个输出代码: (1) 一个 32 位数字滤波高精度低噪声代码;和 (2) 一个 22 位无延迟复合代码。可配置数字滤波器通过对来自 SAR ADC 内核的数据流实施低通滤波和降频采样以降低测量噪声,产生了 32 位滤波输出代码。22 位复合代码由一个代表差分电压的 14 位代码和一个代表共模电压的 8 位代码组成。22 位复合代码可在每个转换周期中提供,并没有延迟周期。

可通过引脚搭接容易地针对 4 种不同的降频采样因子配置数字滤波器。这些配置提供一个 131dB (在 3.9ksps) 和 145dB (在 61sps) 的动态范围。数字低通滤波器放宽了对于模拟抗混迭的要求。采用 SYNC 引脚可以很容易地实现多个 LTC2508-32 器件的同步。

## 转换操作

LTC2508-32 有两类型阶段。在采集阶段中,一个 32 位电荷再分配电容器 D/A 转换器 (CDAC) 连接至 IN+和 IN-引脚,对模拟输入电压进行采样。MCLK 引脚上的脉冲上升沿将启动一个转换。在转换阶段中,利用逐次逼近算法对该32 位 CDAC 进行排序,并对采样输入与基准电压的二进制加权分数 (例如:V<sub>REF</sub>/2,V<sub>REF</sub>/4 ... V<sub>REF</sub>/4294967296)进行有效的比较。在转换结束时,CDAC 的输出近似于采样模拟输入。ADC 控制逻辑电路随后把 32 位数字输出代码传递至数字滤波器以实施进一步处理。把一个代表差分电压的14 位代码和一个代表共模电压的8 位代码组合起来以形成一个22 位复合代码。该22 位复合代码可在每个转换周期中提供,并没有任何延迟周期。

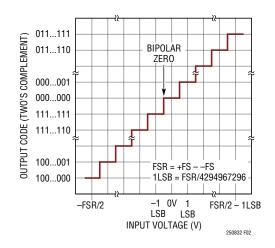

#### 传递函数

LTC2508-32 把  $2 \times V_{REF}$  的全标度差分电压数字化为  $2^{32}$  个电平,从而产生一个 2.3nV 的 LSB 大小和一个 5V 基准。理想的传递函数示于图 2。输出数据为二进制补码格式。

图 2:LTC2508-32 传递函数

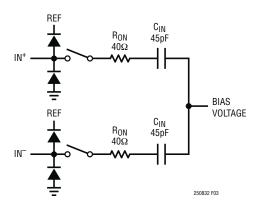

## 模拟输入

LTC2508-32 在宽共模输入范围内对其模拟输入引脚之间的电压差 (IN+ - IN-) 进行采样,同时利用 ADC 的共模抑制比 (CMRR) 对两个输入引脚所共模的无用信号进行衰减。宽共模输入范围搭配高 CMRR 可允许 IN+/IN-模拟输入以一种任意的相互关系摆动,前提是每个引脚的电压保持在GND 和 V<sub>REF</sub> 之间。LTC2508-32 的这一独特特性使其能够接受众多的信号摆幅,包括传统类别的模拟输入信号,例如:伪差分单极、伪差分真正双极和全差分,从而简化了信号链路设计。

在采集阶段中,每个输入都具有串联的约 45pF ( $C_{IN}$ ) 电容和 40Ω ( $R_{ON}$ ) 电阻,前者来自采样电路,而后者则来自采样开关的导通电阻。

LINEAR TECHNOLOGY

图 3:LTC2508-32 差分模拟输入的等效电路

在采样期间,输入吸收一个电流尖峰并对  $C_{IN}$  电容器进行充电。在转换期间,模拟输入仅吸收很小的漏电流。

### 输入驱动电路

一个低阻抗信号源能直接驱动 LTC2508-32 的高阻抗输入,并不会产生增益误差。应该对一个高阻抗信号源进行缓冲,以最大限度地缩减采集期间的稳定时间,从而优化 ADC 的线性。为了获得最佳性能,应采用一个缓冲放大器来驱动 LTC2508-32 的模拟输入。该放大器提供了低输出阻抗,从而在采集阶段中实现了模拟信号的快速稳定。另外,它还在信号源与 ADC 输入电流之间提供了隔离。

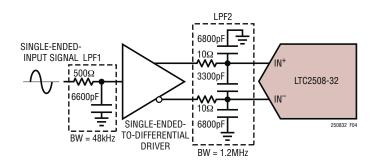

## 噪声和失真

必须考虑输入缓冲放大器和其他支持电路的噪声和失真,因为它们会导致 ADC 噪声和失真的增加。应采用一个低带宽滤波器在缓冲放大器之前对含有噪声的输入信号进行滤波,以最大限度地降低噪声。对于许多应用而言,使用一个图 4 所示的简单单极点 RC 低通滤波器 (LPF1) 就足够了。

应在缓冲器和 ADC 输入之间采用一个耦合滤波器网络 (LPF2), 旨在尽量地抑制因采样瞬变而反射至缓冲器中的 扰动。如果模拟输入端上的 RC 时间常数很大,则将减缓模拟输入的稳定速度。因此,LPF2 通常需要一个比 LPF1 更

大的带宽。另外,该滤波器还有助于极大地降低缓冲器所产生的噪声。必须选择一个具低噪声密度的缓冲放大器,以最大限度地减轻 SNR 指标的劣化。

图 4:对输入信号进行滤波

在 RC 滤波器中应使用高质量的电容器和电阻器,因为这些器件会增加失真。NPO 和银云母型介质电容器具有卓越的线性度。表面贴装型碳质电阻器会由于其自发热及焊接过程中可能出现的损坏而产生失真。表面贴装型金属膜电阻器对于上述两种问题的敏感度都低得多。

#### 输入电流

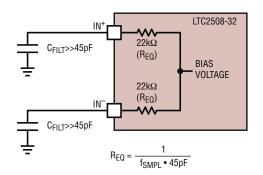

在把一个放大器耦合至 LTC2508-32 时的一项重要考虑是处理 ADC 输入在每个采集阶段的起点所吸收的电流尖峰。 ADC 输入可被模拟为驱动电路的一个开关电容器负载。驱动电路可能部分依赖于利用直接布设在 ADC 输入端上的小滤波电容器 CFILT 来衰减开关电容器电流尖峰,同时部分依赖于驱动放大器拥有足够的带宽以从剩余扰动实现恢复。专为 DC 性能而优化的放大器也许不具备在 ADC 的最大转换速率下实现完全恢复所需的充足带宽,这会产生非线性和其他误差。耦合滤波器电路可以划分为三大类:

完全稳定 — 该场合的特性是滤波器时间常数以及一个比采样周期短得多的总稳定时间。当采集开始时,对耦合滤波器产生扰动。对于典型的一阶 RC 滤波器而言,这种扰动将看似一个具指数式衰减的初始阶跃。放大器将具有其针对该扰动的独特响应,这有可能包括振铃。如果输入完全地稳定(至 LTC2508-32 的准确度以内),则扰动将不会产生任何误差。

部分稳定 — 在该场合中,采集的开始将引起耦合滤波器的扰动,其随后开始稳定至接近标称输入电压。然而,在输入稳定至其终值之前采集将终止 (而转换操作随之开始)。这通常会产生一个增益误差,但只要稳定过程是线性的,就不会产生失真。耦合滤波器的响应受放大器的输出阻抗和其他参数的影响。对于高精度、低带宽放大器,不能总是假定可实现针对快速开关电容器电流尖峰的线性稳定响应。耦合滤波器所起的作用是在电流尖峰的高频能量到达放大器之前对其实施衰减。

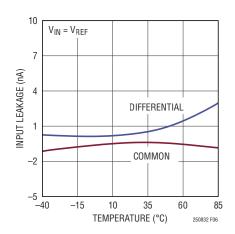

另外,在设计输入驱动电路时还应考虑 LTC2508-32 的输入漏电流,因为源阻抗将把输入漏电流转换为一个附加的输入电压误差。在整个工作温度范围内,输入漏电流 (共模和差分) 通常极小。图 6 示出了一款典型器件在整个温度范围内的输入漏电流。

图 5: LTC2508-32 之差分 模拟输入的等效电路 (在 1Msps)

图 6:整个温度范围内的 共模和差分输入漏电流

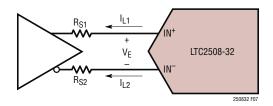

设  $R_{S1}$  和  $R_{S2}$  为图 7 所示差分输入驱动电路的源阻抗,并设  $I_{L1}$  和  $I_{L2}$  为流出 ADC 模拟输入端的漏电流。由漏电流引起的差分电压误差  $V_F$  可用下式来表达:

$$V_{E} = \frac{R_{S1} + R_{S2}}{2} \bullet (I_{L1} - I_{L2}) + (R_{S1} - R_{S2}) \bullet \frac{I_{L1} + I_{L2}}{2}$$

在整个工作温度范围和共模输入电压范围内,共模输入漏电流  $(I_{L1} + I_{L2})/2$  通常极小 (图 6)。于是,源阻抗  $R_{S1}$  和  $R_{S2}$  的任何合理失配 (5% 以下) 都将只引起一个可以忽略的误差。差分漏电流通常也是非常小,而其非线性成分则更小。只有非线性成分将影响 ADC 的线性度。

LINEAR TECHNOLOGY

2508321

图 7:驱动器的源阻抗和 LTC2508-32 的输入漏电流

为了获得最佳性能,建议源阻抗  $R_{S1}$  和  $R_{S2}$  介于  $5\Omega$  和  $50\Omega$  之间,并具有 1% 的容差。对于处在该范围之中的源阻抗, $R_{S1}$ 和  $R_{S2}$  的电压和温度系数往往并不是至关重要的。被测试保证的 AC 和 DC 指标是在采用  $5\Omega$  源阻抗进行测试的,并且由于信号没有完全建立,这些指标会随着源阻抗的增加而逐渐变差。

#### DC 准确度

LTC2508-32 拥有卓越的 INL 指标。这使 LTC2508-32 非常适合那些要求高 DC 准确度 (包括偏移和偏移漂移等参数)的应用。为了在整个 DC 信号链路中保持高准确度,必须非常谨慎地选择放大器。可能需要一个至少 126dB 的大信号开环增益,以确保那些针对增益为 -1 配置的放大器具备1ppm 的线性度。不过,如果放大器的增益特性 (几乎全部)是线性的,那么较小的增益就足够了。对于被配置为单增益

缓冲器的放大器,必须考虑放大器的失调与信号电平的关系。例如:对于一个 5V 摆幅,1ppm 线性度可能要求失调的已知变化幅度小于 5μV。然而,如果关系已知 (几乎全部是) 线性的,则或许可以接受更大的失调变化幅度。单位增益缓冲放大器通常需要给电源轨提供巨大的峰值储备空间以实现最佳的性能。相比于单位增益缓冲放大器,配置用以尽量抑制放大器输入端上摆幅的负输出放大器电路可在峰值储备空间极小的情况下实现更好的工作性能。应谨慎地考虑负输出放大器之反馈网络的线性和热特性,以确保 DC 准确度。

#### 缓冲输入信号

LTC2508-32 的宽共模输入范围和高 CMRR 可允许 IN+和 IN-模拟输入引脚以一种任意的相互关系摆动,前提是每个引脚的电压保持在  $V_{REF}$  和 GND 之间。LTC2508-32 的这一独特特性使其能够接受众多的信号摆幅,从而简化了信号链路设计。

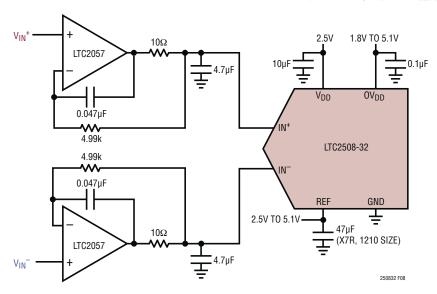

### 缓冲 DC 准确的输入信号

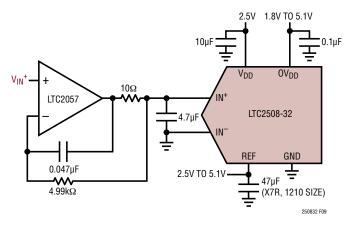

图 8 示出了一款典型应用电路,其采用 LTC2057 对两个模拟输入电压进行缓冲。LTC2057 是一款高精度零漂移放大器,用于对 LTC2508-32 的低偏移和偏移漂移提供补充。该图示出的是同相放大器配置中的 LTC2057。

图 8:缓冲两个模拟输入信号

LTC2508-32 具有  $130\mu V$  的保证最大偏移误差 (典型漂移为  $\pm 0.014ppm/^{\circ}C$ ) 和 150ppm 的保证最大全标度误差 (典型漂移为  $\pm 0.05ppm/^{\circ}C$ )。低漂移对于在校准系统的宽温度范围内保持准确度是很重要的。

#### 缓冲 DC 准确的单端输入信号

虽然图 8 中所示的电路能够缓冲单端输入信号,但是当单端信号基准电平为固有的低阻抗且不需要缓冲时,最好采用图 9 中示出的电路。该电路去除了一个驱动器和一个低通滤波器,从而减少了部件数目和功率耗散,并抑制了由于驱动器噪声所导致的 SNR 性能劣化。

LTC2057 具有超卓的 DC 特性,但是输出电流驱动能力有限,因而导致 THD 性能在输入频率增加时出现下降。把输入频率限制在 10Hz 以保持产品手册规定的完整 THD。

图 9:缓冲单端信号

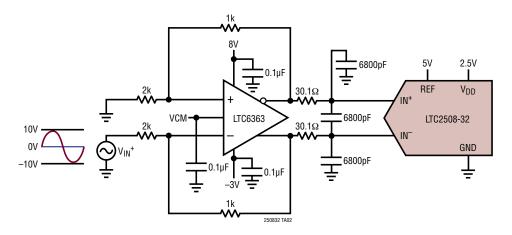

#### 缓冲 AC 输入信号

本产品手册中介绍的许多驱动器电路强调了对于低带宽输入信号的性能,并相应地选择放大器。虽然 LTC2057 的特点是拥有出色的 DC 指标,但是其输出电流驱动能力则是有限的。这限制了 LTC2057 按照 LTC2508-32 产品手册的完整规格所能驱动的输入频率范围。当以 DF = 256 工作时,LTC2508-32 之滤波输出的 -3dB 带宽等于 480Hz。因此,当驱动带宽大于 10Hz 的输入信号时,需要采用一种替代的驱动器解决方案。

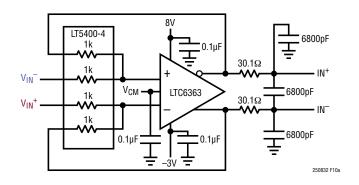

LTC6363 是一款低功率、低噪声、全差分运放,可用于驱动带宽大于 10Hz 的输入信号。LTC6363 可配置以把一个单端输入信号转换为一个差分输出信号,也可以进行差分驱动。

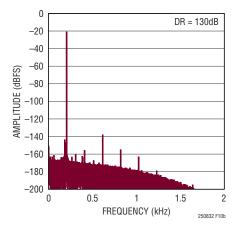

图 10a 示出了采用 LTC6363 以缓冲一个 10V 差分输入信号的情形。在该场合中,该放大器被配置为一个采用 LT5400-4 精准电阻器的单位增益缓冲器。如图 10b 的 FFT 所示,LTC6363 把 LTC2508-32 驱动至接近产品手册宣称的性能水平。

图 10a:缓冲 AC 输入

图 10b:图 10a 所示电路的 128k 点 FFT (f<sub>IN</sub> = 200Hz)

### ADC 基准

一个外部基准规定了 LTC2508-32 的输入范围。一个低噪声、低温度漂移基准对于实现 ADC 的完整产品手册性能指标是至关紧要。凌力尔特公司提供了一个专为满足众多应用的需要而设计的高性能基准产品库。凭借其小尺寸、低功率和高准确度,LTC6655-5 特别适合与 LTC2508-32 一起使用。LTC6655-5 可提供 0.025% (最大值) 的初始准确度和2ppm/°C (最大值) 的温度系数,适合高精度应用。

当选择一个用于 LTC6655-5 的旁路电容器时,应谨慎地考虑该电容器的电压额定值、温度额定值和封装尺寸。物理尺寸较大并具有较高电压和温度额定值的电容器往往可提供一个较大的有效电容,能更好地对 LTC6655-5 的噪声进行滤波,从而产生一个较高的 SNR。因此,建议利用一个靠近REF 引脚的 47μF 陶瓷电容器 (电介质为 X7R,尺寸为1210,10V 额定电压) 对 LTC6655-5 进行旁路。

在每个转换周期中,LTC2508-32 的 REF 引脚从该  $47\mu$ F 旁路电容器吸收电荷 ( $Q_{CONV}$ )。基准利用一个平均电流 ( $I_{REF} = Q_{CONV}/t_{CYC}$ ) 来补充该电荷。从 REF 引脚吸收的电流  $I_{REF}$  取决于采样速率和输出代码。如果 LTC2508-32 以恒定速率对某个信号进行连续采样,则 LTC6655-5 将在整个代码范围内把基准电压的偏差保持在 < 0.5 ppm。

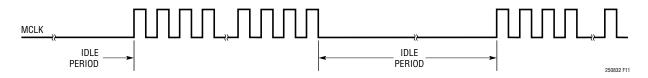

当空载时,LTC2508-32 的 REF 引脚仅吸收一个很小的漏电流 (<1μA)。在那些经历了漫长的空载周期之后获取一组样本的应用中 (如图 11 所示),I<sub>REF</sub> 迅速地从大约 0μA 变至 1mA 的最大值 (在 1Msps)。平均吸收电流的这一阶跃在基准中引发了一个瞬态响应,必须对此加以考虑,因为基准输出电压中的任何偏差都将影响输出代码的准确度。在重视基准瞬态响应的应用中,同样建议使用具有快速稳定特性的 LTC6655-5 基准。

#### 基准噪声

降频采样因子 (DF) 每增加 4 倍,ADC 的动态范围将增加约 6dB。SNR 也应以相同的方式作为 DF 的一个函数而改善。然而,对于接近全标度的大输入信号,任何基准噪声在 DF 增大的情况下都将限制 SNR 的改善,因为 REF 引脚上的任何噪声均将在输入信号的基本频率周围调制。因此,至关重要的是采用一个低噪声基准,特别是假如输入信号幅度接近全标度。对于小输入信号,动态范围将如本节先前描述的那样有所改善。

### 动态性能

采用快速傅立叶变换 (FFT) 技术来测试额定吞吐量条件下 ADC 的频率响应、失真和噪声。通过施加一个低失真正弦

图 11:显示突发采样的 MCLK 波形

波并采用一种 FFT 算法来分析数字输出,可检查 ADC 频谱成分中超出基频之外的频率情况。LTC2508-32 为 AC 失真及噪声测量均提供了保证测试限值。

#### 动态范围

动态范围是全标度输入的 RMS 值与输入短接至  $V_{REF}/2$  时测量的总 RMS 噪声之比。DF=256 时 LTC2508-32 的动态范围为 131dB,它随着降频采样因子的增大而改善。

## 信号与噪声加失真之比 (SINAD)

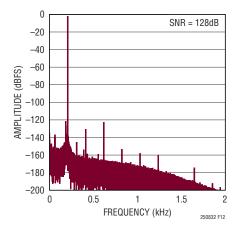

信号与噪声加失真之比 (SINAD) 是输入基频的 RMS 幅度与 ADC 输出端上的所有其他频率分量的 RMS 幅度之比。输出被带限至从高于 DC 至低于半采样频率之间的频带内。如图 12 所示,LTC2508-32 在 1MHz 采样速率及 200Hz输入和 DF = 256 的情况下实现了一个 120dB 的典型 SINAD。

图 12: LTC2508-32 的 128k 点 FFT 曲线图 (DF = 256、f<sub>IN</sub> = 200Hz 和 f<sub>SMPL</sub> = 1MHz)

### 信噪比 (SNR)

信噪比 (SNR) 是输入基频的 RMS 幅度与除了首五个谐波和 DC 之外所有其他频率分量的 RMS 幅度之比。如图 12 所示,LTC2508-32 在以 1MHz 采样速率对一个 200Hz 输入进行采样且 DF = 256 的情况下实现了一个 125dB 的 SNR。

## 总谐波失真 (THD)

总谐波失真 (THD) 是输入信号所有谐波的 RMS 之和与基频自身之比。带外谐波混入介于 DC 和半采样频率 (f<sub>SMPI</sub>/2) 之间的频带。THD 由下式来表示:

THD =

$$20LOG \frac{\sqrt{V2^2 + V3^2 + V4^2 + \dots + VN^2}}{V1}$$

式中的 V1 为基频的 RMS 幅度,V2 至 VN 为二次至 N 次 谐波的幅度。

### 电源考虑

LTC2508-32 具有两个电源引脚:2.5V 电源  $(V_{DD})$  和数字输入 / 输出接口电源  $(OV_{DD})$ 。灵活的  $OV_{DD}$  电源允许 LTC2508-32 与任何工作电压介于 1.8V 和 5V 之间的任何数字逻辑电路 (包括 2.5V 和 3.3V 系统) 进行通信。

#### 电源排序

LTC2508-32 没有任何特殊的电源排序要求。应谨慎地遵守「绝对最大额定值」部分中所描述的最大电压关系。LTC2508-32 具有一个上电复位 (POR) 电路,在初始上电或电源电压降至 1V 以下时,此电路将使 LTC2508-32 复位。当电源电压重新进入标称电源电压范围时,POR 将重新预置 ADC。在一个 POR 过程之后的 200µs 之内,不得启动转换操作以确保重新初始化周期已经结束。在此时点之前启动的任何转换都将产生无效的结果。

## 定时和控制

#### MCLK 定时

MCLK 上的一个上升沿将给 LTC2508-32 上电并起动一个转换。一旦某个转换已被启动,那么在该转换完成之前 MCLK 上进一步的转换将被忽略。为获得最佳结果,MCLK 的下降沿应在转换启动后的 40ns 之内出现。为了实现最佳

LINEAD

性能,MCLK 应利用一个乾净的低抖动信号来驱动。转换器状态由 BUSY 输出指示,当转换在进行之中时该输出处于高电平。转换操作一旦完成,LTC2508-32 将断电并开始采集输入信号以执行下一个转换。

#### 内部转换时钟

LTC2508-32 具有内部定时电路,该电路经过修整以实现一个 652ns 的最大转换时间。凭借 1Msps 的最大采样速率,可在无需任何外部调整的情况下保证 335ns 的最小采集时间。

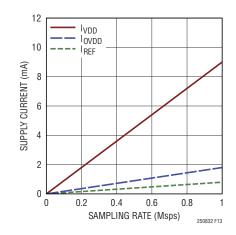

#### 自动断电

LTC2508-32 在一个转换完成之后自动断电,并当一个新的转换在 MCLK 的上升沿上启动时自动上电。在断电期间,来自最后一个转换的数据可由时钟同步输出。如需尽可能地降低断电期间的功率耗散,则停用 SDOA、SDOB 并关断 SCKA、SCKB。自动断电功能将在采样速率降低时减少 LTC2508-32 的功耗。由于只在转换操作期间消耗功率,因此在低采样速率下 LTC2508-32 于转换周期 (t<sub>CYC</sub>) 的大部分时间里处于断电状态,从而减低了随采样速率而调节的平均功耗,如图 13 所示。

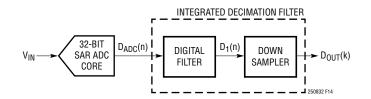

#### 抽取滤波器

许多 ADC 应用运用数字滤波方法来降低噪声。实现一个数字滤波器通常需要一个 FPGA 或 DSP。LTC2508-32 具有一个能够在无需任何附加硬件的情况下提供 4 种可选数字滤波功能的集成型抽取滤波器,因而简化了应用解决方案。图 14 示出了 LTC2508-32 数字滤波输出信号通路,其中32 位 SAR ADC 内核的输出 DADC(n) 被传递给该集成型抽取滤波器。

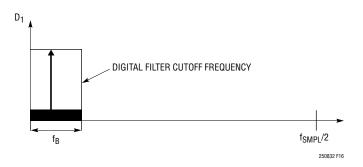

#### 数字滤波

以一个  $f_{SMPL}$  的速率对 LTC2508-32 的输入进行采样,并以该速率把数字字  $D_{ADC}(n)$  传输至数字滤波器。32 位 SAR ADC 内核产生的噪声均匀地分布在从 DC 至  $f_{SMPL}$  的频率范围内。图 15 示出了 SAR ADC 内核输出端上的  $D_{ADC}(n)$  频谱。在该例中,关注的带宽  $f_{B}$  是  $f_{SMPL}/2$  的一小部分。

图 13:LTC2508-32 的电源电流与 采样速率的关系曲线

图 14: LTC2508-32 数字滤波输出信号通路

图 15:SAR ADC 内核输出的频谱

图 16:数字滤波器内核输出的频谱

LTC2508-32 中集成的数字滤波器可抑制带外噪声功率,从 而降低总噪声和增加动态范围 (DR)。滤波器带宽越低,噪声就越低,而且 DR 越高。图 16 示出了数字滤波器输出端上 D<sub>1</sub>(n) 的对应频谱,这里,由数字滤波器对超过截止频率的噪声进行抑制。

#### 隆频采样

由一个降频采样器降低数字滤波器的输出数据速率,并不会在关注的带宽中引脚频谱干扰。

该降频采样器通过把每第 DF 个样本传递至输出、并丢弃所有其他的样本来降低数据速率。降频采样器输出端上的采样频率  $f_0 = f_{SMPI}$  与 DF 之比,即: $f_0 = f_{SMPI}$  /DF。

LTC2508-32 使得用户能够根据某个期望的关注带宽来选择 DF。可通过对引脚 SEL0 和 SEL1 进行引脚搭接来选择 4 种可用的配置。表 1 汇总了不同的抽取滤波器配置和特性。

### 混迭

一个被采样的信号所能拥有和被其样本准确地代表的最大带宽是奈奎斯特带宽。奈奎斯特带宽的范围从 DC 至半采样频

率 (又称「奈奎斯特频率」)。一个带宽超过奈奎斯特频率 的输入信号在被采样时将出现失真,该失真是由一种被称为 「混迭」的效应引起的。

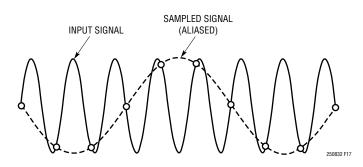

当混迭时,大于奈奎斯特频率的频率分量将经历频移并出现在奈奎斯特带宽之内。图 17 示出了时域中的混迭。实线表示一个频率大于奈奎斯特频率 (f<sub>0</sub>/2) 的正弦波输入信号。圆圈表示以 f<sub>0</sub> 进行采样的信号。请注意,被采样的信号等同于对另一个具较低频率之正弦波输入信号的采样 (用虚线表示)。为消除混迭,需要在对输入信号实施采样之前将其带限至奈奎斯特带宽。一个用于抑制位于奈奎斯特带宽以外的频谱分量的滤波器被称为「抗混迭滤波器」(AAF)。

#### 抗混迭滤波器

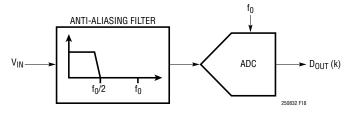

图 18 示出了一个典型的信号链路,其包括一个低通 AAF 和一个采样频率为  $f_0$  的 ADC。AAF 抑制频率超过  $f_0/2$  的输入信号分量,从而避免发生混迭。如果关注的带宽接近  $f_0/2$ ,则 AAF 必须具备非常陡的滚降。模拟 AAF 的复杂性 随着滚降的陡峭度增加,而且在需要一个滚降非常陡峭的滤波器时可能根本无法使用 AAF。

图 17: 抗混迭的时域视图

表 1:LTC2508-12 中的滤波器之特性

| SEL1:SEL0 | 降频采样因 <del>子</del><br>(DF) | 当 f <sub>SMPL</sub> = 1MHz 时的<br>-3dB 带宽 | 当 f <sub>SMPL</sub> = 1MHz 时的<br>输出数据速率 (ODR) | 动态范围    |

|-----------|----------------------------|------------------------------------------|-----------------------------------------------|---------|

| 00        | 256                        | 480Hz                                    | 3906sps                                       | 131dB   |

| 01        | 1024                       | 120Hz                                    | 796sps                                        | 136dB   |

| 10        | 4096                       | 30Hz                                     | 244sps                                        | 141dB   |

| 11        | 16384                      | 7.5Hz                                    | 61sps                                         | 145dB   |

|           |                            |                                          |                                               | 250832f |

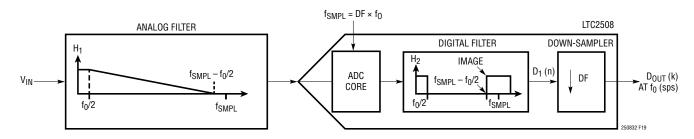

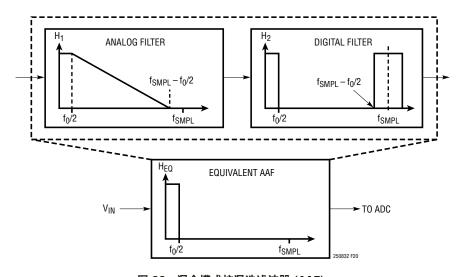

或者,也可以组合使用一个简单的低阶模拟滤波器和一个数字滤波器,以产生一个具非常陡峭之滚降的混合模式等效 AAF。图 19 示出了一种混合模式滤波器实现方案,这里,在一个具平缓滚降的模拟滤波器之后布设了采样频率为  $f_{SMPL} = DF \bullet f_0$  的 LTC2508-32。LTC2508-32 在 ADC 内核的输出端上具有一个集成的数字滤波器。如图 20 所示,等效 AAF  $H_{EQ}(f)$  是模拟滤波器  $H_1(f)$  和数字滤波器  $H_2(f)$  的频率响应之乘积。数字滤波器提供陡峭的滚降,从而允许模拟滤波器具有相对平缓的滚降。

LTC2508-32 中的数字滤波器工作在 ADC 采样频率  $f_{SMPL}$ ,并抑制频率超过  $f_{0}/2$  的信号。数字滤波器  $H_{2}(f)$  的频率响应在  $f_{SMPL}$  的倍数处重复,因而在  $f_{SMPL}$  的每个倍数频率上产生不希望有的通带。模拟滤波器的设计应提供针对无用通带的足够抑制,以使  $H_{EQ}(f)$  仅具有一个与所关注的频率范围相对应的通带。较大的 DF 设定值对应于较小的数字滤波器带宽,从而为模拟滤波器具有更加平缓的滚降创造了条件。一个简单的一阶或二阶模拟滤波器将为大多数系统提供足够的抑制。

图 18: 具 AAF 的 ADC 信号链路

图 19:混合模式滤波器信号链路

图 20:混合模式抗混迭滤波器 (AAF)

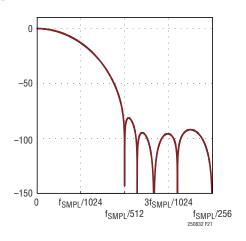

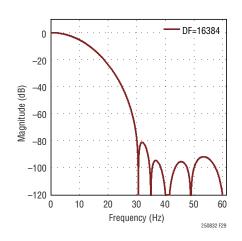

图 21:数字滤波器的频率响应 (DF = 256)

#### 数字滤波器的频率响应

图 21 示出了当 LTC2508-32 被配置为在 DF = 256 和采样 频率 =  $f_{SMPl}$  条件下工作时数字滤波器的频率响应。

对于 LTC2508-32 的每种配置,数字滤波器是一个具线性相位响应的低通有限脉冲响应 (FIR) 滤波器。带宽与所选的 DF 值成反比。每种配置为处于  $f_0/2$  和  $f_{SMPL} - f_0/2$  范围内的频率提供最小 80dB 的衰减。4 种数字滤波器配置的滤

波器系数和频率响应的详细版本可通过 www.linear.com/docs/52896 获得。表 2 列出了每个数字滤波器之脉冲响应的长度和群延迟。

表 2: 数字滤波器的长度

| 降频采样因子<br>(DF) | 数字滤波器脉冲<br>响应的长度 | 群延迟<br>(f <sub>SMPL</sub> = 1Msps) |

|----------------|------------------|------------------------------------|

| 256            | 2,304            | 1.2ms                              |

| 1,024          | 9,216            | 4.6ms                              |

| 4,096          | 36,864           | 18.4ms                             |

| 16,384         | 147,456          | 73.7ms                             |

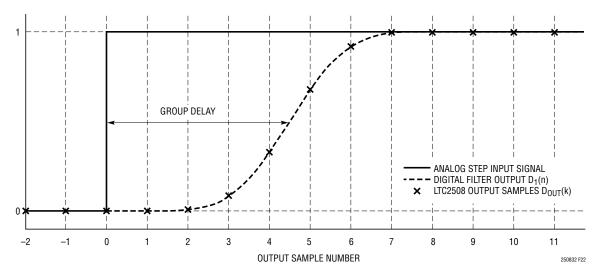

#### 稳定时间和群延迟

每个数字滤波器之脉冲响应的长度决定了其稳定时间。线性相位滤波器呈现恒定的「延迟时间与输入频率的关系」 (即:恒定的群延迟)。数字滤波器的群延迟被定义为至脉冲响应之中心的延迟。

LTC2508-32 专为低延迟而优化,而且它提供了快速稳定。图 22 示出了 LTC2508-32 之模拟输入端上的一个阶跃变化后的输出稳定运行方式。X 轴的单位为输出样本数目。阶跃响应是所有 DF 数值的代表。完全的稳定在 10 个输出样本内实现。

图 22:LTC2508-32 的阶跃响应

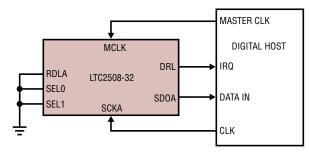

## 数字接口

LTC2508-32 具有两个数字串行接口。串行接口 A 用于读取滤波输出数据。串行接口 B 用于读取无延迟输出数据。这两个接口均支持一个灵活的 OV<sub>DD</sub> 电源,因而允许 LTC2508-32 与任何工作电压介于 1.8V 和 5V 之间的任何数字逻辑电路 (包括 2.5V 和 3.3V 系统) 进行通信。

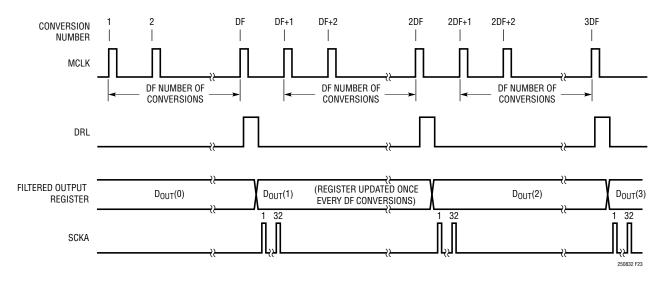

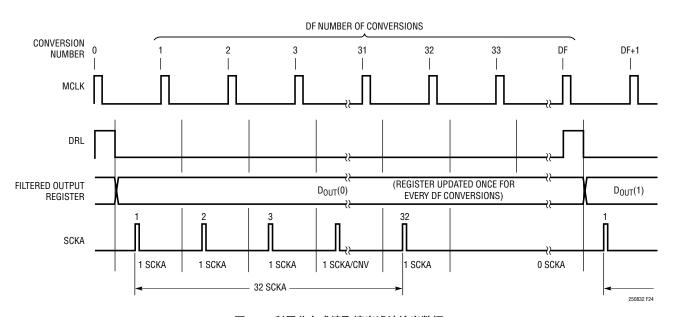

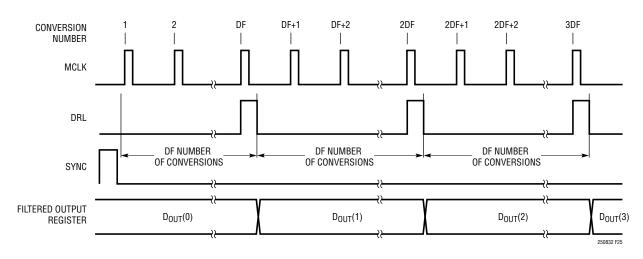

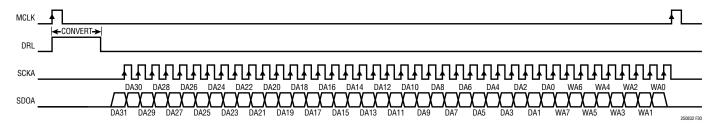

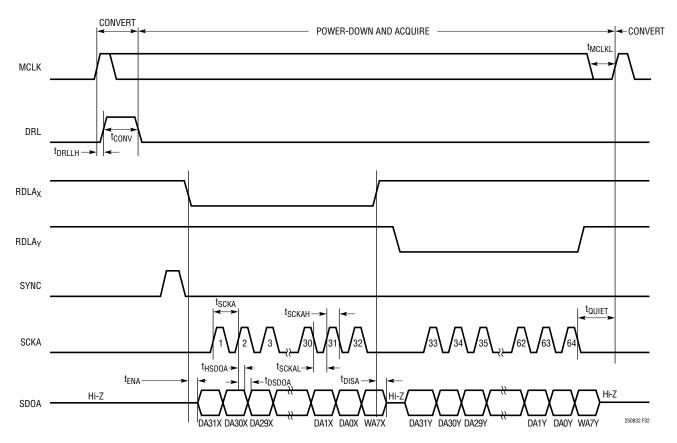

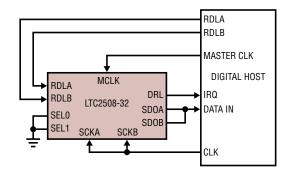

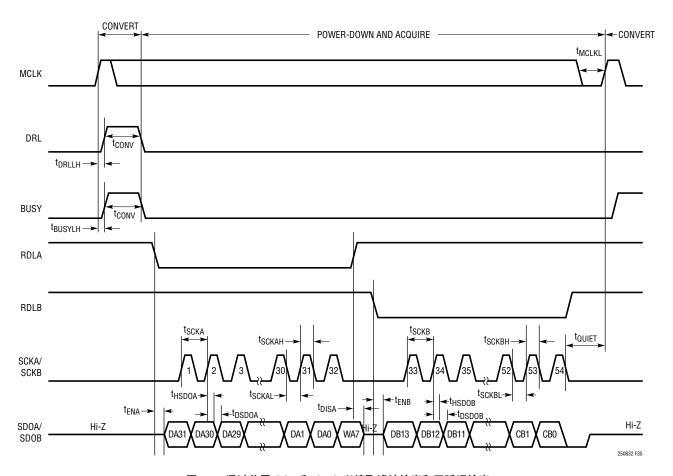

#### 滤波输出数据

图 23 示出了用于读取滤波输出数据的典型操作。I/O 寄存器包含由抽取滤波器提供的滤波输出代码  $D_{OUT}(k)$ 。  $D_{OUT}(k)$  每 DF 个转换周期更新一次。当  $D_{OUT}(k)$  被更新时,一个定时信号 DRL 发出指示。DRL 在每第 DF 个转换的起点变至高电平,并在转换结束时变至低电平。 $D_{OUT}(k)$ 的 32 位可在下一个 A/D 转换开始之前读出。

图 23:典型滤波输出数据操作时序

图 24:利用分布式读取读出滤波输出数据

## 分布式读取

LTC2508-32 使得用户能在多个转换期间读出 I/O 寄存器的内容。图 24 示出了一种对于所有 32 个连续的 A/D 转换各读取一位 D<sub>OUT</sub>(k) 的情形,因而允许使用一个速度慢得多的串行时钟 (SCKA)。在 A/D 转换操作期间 (当 BUSY 为高电平时) 应避免在数字接口上发生转换。

### 同步

数字滤波器  $D_1(n)$  的输出每个转换更新一次,而降频采样器输出  $D_{OUT}(k)$  则是每 DF 个转换更新一次。同步是选择何时更新输出  $D_{OUT}(k)$  的过程。

这是通过在 LTC2508-32 的 SYNC 引脚上施加一个脉冲来完成的。如图 25 所示,在提供了一个 SYNC 脉冲之后,用于  $D_{OUT}(k)$  的 I/O 寄存器在 DF 个转换的每个倍数上更新。当  $D_{OUT}(k)$  被更新时,一个定时信号 DRL 发出指示。

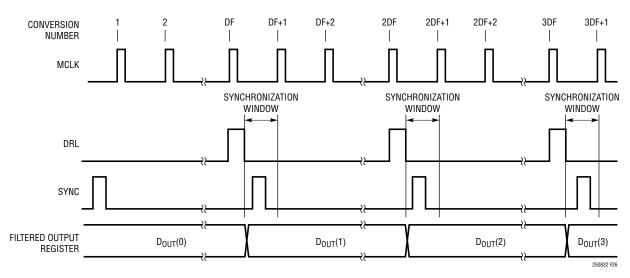

SYNC 功能可使多个依靠同一个主时钟工作并采用公共 SYNC 信号的 LTC2508 器件实现彼此之间的同步。这允许 每个 LTC2508 器件同时更新其输出寄存器。请注意,所有 正在被同步的器件必须采用相同的 DF 进行操作。

图 25:采用单个 SYNC 脉冲的同步

## 周期同步

强化一个现有同步的 SYNC 脉冲不会干扰正常操作。图 26 示出了一种对每 DF 个转换施加一个 SYNC 脉冲以持续强化同步的情形。图 26 标示了可施加一个 SYNC 脉冲以强化同步操作时的同步窗口。

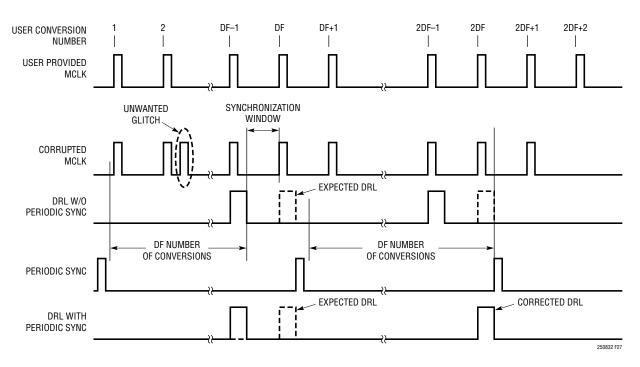

### 自校正同步

图 27 示出了 MCLK 上的意外毛刺干扰导致执行一个额外 A/D 转换的情形。这个额外的转换改变了 D<sub>OUT</sub>(k) 的更新瞬间。施加的周期 SYNC 脉冲重新建立了期望的同步并在一个转换周期之内完成自校正。请注意,当同步变更 (重新建立) 时数字滤波器复位。

图 26:采用一个周期 SYNC 脉冲的同步

图 27: 从意外毛刺干扰恢复同步

图 28:典型奈奎斯特输出数据操作时序

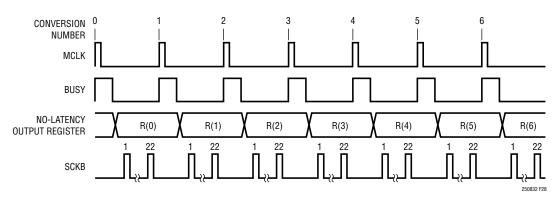

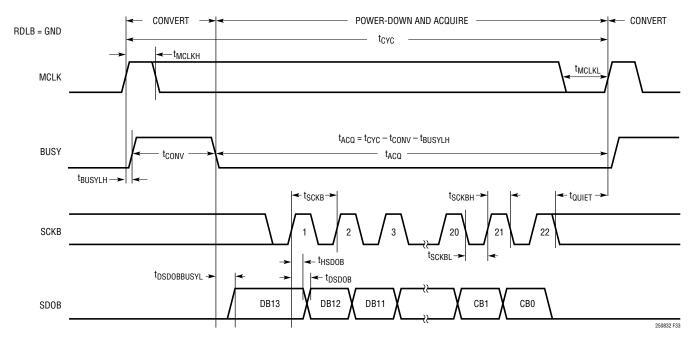

### 无延迟输出数据

图 28 示出了用于读取无延迟输出数据的典型操作。无延迟 I/O 寄存器保存了一个在 MCLK 的上升沿从取自输入 IN+和 IN-的最新样本获得的 22 位复合代码 R(n)。R(n) 的首 14 个位代表输入电压差  $(IN^+ - IN^-)$ ,MSB 优先。末 8 位代表共模输入电压  $(IN^+ + IN^-)/2$ ,MSB 优先。

图 29:数字滤波器的频率响应 (DF = 16384)

#### 50Hz 和 60Hz 抑制

图 29 示出了 LTC2508-32 中配置为在 DF = 16384 和  $f_{SMPL}$  = 1Msps 条件下工作的数字滤波器之频率响应。如图所示,获得了 50Hz 和 60Hz 的至少 100dB 同时抑制。需注意的是,图 29 所示的频率轴随  $f_{SMPL}$  而调节。

#### 配置字

一个 8 位配置字 WA[7:0] 被附加到 SDOA 上的 32 位输出代码,以产生一个 40 位的总输出字,如图 30 所示。该配置字指定了数字滤波器被配置为采用哪个降频采样因子(DF)进行操作。由时钟同步输出该配置字是任选的。表 3 列出了针对每个 DF 值的配置字。

表3:对于不同 DF 值的配置字

| DF     | WA[ <b>7:0</b> ] |

|--------|------------------|

| 256    | 10000101         |

| 1,024  | 10100101         |

| 4,096  | 11000101         |

| 16,384 | 11100101         |

图 30:采用 LTC2508-32 以读取滤波输出

## 滤波输出数据,单个器件,DF = 256

图 31 示出了一个被配置为在 DF = 256 的条件下运作的 LTC2508-32。当 RDLA 接地时,SDOA 被使能,而且输出 结果的 MSB (DA31) 可在 DRL 下降沿之后  $t_{DSDOADRLL}$  提供。

图 31:采用单个 LTC2508-32 (DF = 256) 以读取滤波输出

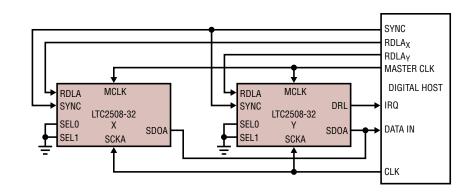

#### 滤波输出数据,多个器件, DF = 256

图 32 示出了两个被配置为在 DF = 256 的条件下运作、并 共用 MCLK、SYNC、SCKA 和 SDOA 的 LTC2508-32 器 件。通过共用 MCLK、SYNC、SCKA 和 SDOA,并行运作 多个 ADC 所需信号的数目有所减少。由于 SDOA 是共用 的,因此必须使用每个 ADC 的 RDLA 输入,以一次仅允许一个 LTC2508-32 驱动 SDOA,旨在避免总线冲突。如图 32 所示,RDLA 输入在空载时处于高电平,并在转换操作之间被个别地拉至低电平以从每个器件读出数据。当 RDLA 被拉至低电平时,选定器件的 MSB 在 SDOA 上输出。

图 32:读取滤波输出 (多个器件共用 MCLK、SCKA 和 SDOA)

LINEAR TECHNOLOGY

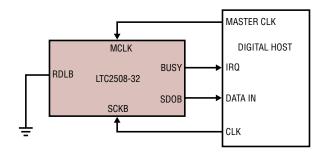

## 无延迟输出数据,单个器件

图 33 示出了单个被配置为读取无延迟数据输出的 LTC2508-32。当 RDLB 接地时,SDOB 被使能,而且输出 结果的 MSB (DB13) 可在 BUSY 下降沿之后 t<sub>DSDOBBUSYL</sub> 提供。

图 33: 采用单个 LTC2508-32 以读取无延迟输出

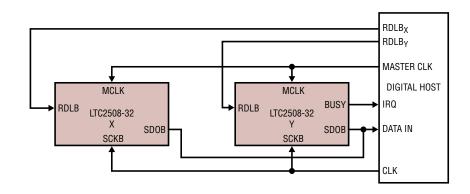

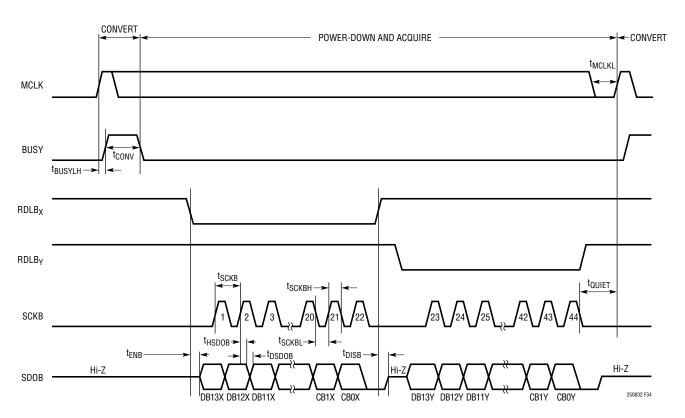

#### 无延迟输出数据,多个器件

图 34 示出了多个被配置为读取无延迟数据输出、并共用 MCLK、SCKB 和 SDOB 的 LTC2508-32 器件。通过共用 MCLK、SCKB 和 SDOB,并行运作多个 ADC 所需信号的 数目有所减少。由于 SDOB 是共用的,因此必须使用每个

ADC 的 RDLB 输入,以一次仅允许一个 LTC2508-32 驱动 SDOB,旨在避免总线冲突。如图 34 所示,RDLB 输入在 空载时处于高电平,并在转换操作之间被个别地拉至低电平 以从每个器件读出数据。当 RDLB 被拉至低电平时,选定器件的 MSB 在 SDOB 上输出。

图 34:读取无延迟输出 (多个器件共用 MCLK、SCKB 和 SDOB)

LINEAR TECHNOLOGY

#### 滤波输出数据,无延迟数据,单个器件

图 35 示出了单个被配置为读取滤波和无延迟输出数据、并 共 用 S D O A 和 S D O B 以 及 S C K A 和 S C K B 的 LTC2508-32。共用信号减少了从 ADC 读取滤波和无延迟数据所需信号的总数。由于 SDOA 和 SDOB 是共用的,因此必须使用 ADC 的 RDLA 和 RDLB 输入,以一次仅允许一个输出驱动共用的 SDO 总线,旨在避免总线冲突。如图

35 所示,RDLA 和 RDLB 输入在空载时处于高电平,并在数据可用时被个别地拉至低电平以从每个串行输出读取数据。当 RDLA 被拉至低电平时,来自 SDOA 的滤波输出数据的 MSB 在共用的 SDO 总线上输出。当 RDLB 被拉至低电平时,从 SDOB 输出之无延迟数据的 MSB 在共用的 SDO 总线上输出。

图 35:通过共用 SCK 和 SDO 以读取滤波输出和无延迟输出

## 电路板佈局

为了获得 LTC2508-32 的最佳性能,建议使用一个四层印刷电路板 (PCB)。PCB 的布局应确保数字和模拟信号线是尽可能分开的。特别地,应注意不要沿着模拟信号迹线或在ADC 的下方排布任何的数字时钟或信号走线。

电源旁路电容器应布设在尽可能靠近电源引脚的地方。用于这些旁路电容器的低阻抗公共回线对于实现 ADC 的低噪声操作是不可或缺的。为此建议采用单个连续且不间断的接地平面。在可能的情况下采用接地对模拟输入走线进行屏蔽。

#### 参考设计

如需了解针对该转换器之参考设计的细节 (包括原理图和 PCB 布局),请查阅 DC2222 (用于 LTC2508-32 的评估套件)的相关资料。DC2222 专为实现 LTC2508-32 的完整产品手册性能而设计。客户电路板布局应尽可能接近地拷贝 DC2222 接地和旁路电容器的安置方案。

## 封装描述

如需了解最近的封装图样,请登录 http://www.linear.com.cn/product/LTC2508-32#packaging

## DKD 封装 24 引脚塑料 DFN (7mm×4mm)

(参考 LTC DWG # 05-08-1864 Rev Ø)

RECOMMENDED SOLDER PAD LAYOUT APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

- 1. DRAWING PROPOSED TO BE MADE VARIATION OF VERSION (WXXX) IN JEDEC PACKAGE OUTLINE MO-229

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

- MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

## 典型应用

### 缓冲和转换一个 ±10V 真正双极输入信号至一个全差分 ADC 输入

## 相关器件

| 器件型号                                     | 描述                                                    | 备注                                                                      |

|------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------|

| LTC2380-24                               | 24 位、1.5/2Msps、±0.5ppm INL 串行、<br>低功率 ADC             | 2.5V 电源, ±5V 全差分输入,100dB SNR,MSOP-16 和<br>4mm x 3mm DFN-16 封装           |

| LTC2368-24                               | 具单极输入范围的 24 位、1Msps、<br>±0.5ppm INL 串行、低功率 ADC        | 2.5V 电源,0V 至 5V 全单极输入,98dB SNR,MSOP-16 和<br>4mm x 3mm DFN-16 封装         |

| LTC2378-20/<br>LTC2377-20/<br>LTC2376-20 | 20 位、1Msps/500ksps/250ksps、<br>±0.5ppm INL 串行、低功率 ADC | 2.5V 电源,±5V 全差分输入,104dB SNR,MSOP-16 和<br>4mm x 3mm DFN-16 封装            |

| DAC                                      |                                                       | •                                                                       |

| LTC2757                                  | 18 位、单通道并行 I <sub>OUT</sub> SoftSpan™                 | ±1LSB INL/DNL,软件可选的范围,7mm x 7mm LQFP-48 封装                              |

| LTC2641                                  | 16 位/14 位/12 位单通道串行 V <sub>OUT</sub> DAC              | ±1LSB INL/DNL, MSOP-8 封装, 0V 至 5V 输出                                    |

| LTC2630                                  | 12 位/10 位/8 位单通道 V <sub>OUT</sub> DAC                 | SC70 6 引脚封装 <sup>,</sup> 内部基准 <sup>,</sup> ±1LSB INL (12 位)             |

| 基准                                       |                                                       |                                                                         |

| LTC6655                                  | 高精度低漂移低噪声缓冲基准                                         | 5V/4.906V/3.3V/3V/2.5V/2.048V/1.25V,2ppm/°C,<br>0.25ppm 峰至峰噪声,MSOP-8 封装 |

| LTC6652                                  | 高精度低漂移低噪声缓冲基准                                         | 5V/4.906V/3.3V/3V/2.5V/2.048V/1.25V,5ppm/°C,<br>2.1ppm 峰至峰噪声,MSOP-8 封装  |

| 放大器                                      |                                                       |                                                                         |

| LTC2057                                  | 低噪声零漂移运算放大器                                           | 4μV 失调电压, 0.015μV/°C 失调电压漂移                                             |

| LTC6363                                  | 低功率、全差分输出放大器 / 驱动器                                    | 2.8V 至 11V 单电源,1.9mA 电源电流,MSOP-8 和 2mm x 3mm<br>DFN-8 封装                |

| LTC6362                                  | 低功率、全差分输入/输出放大器/驱动器                                   | 2.8V 至 5.25V 单电源,1mA 电源电流,MSOP-8 和 3mm x 3mm<br>DFN-8 封装                |