# Multichannel ADC, DACs and Temperature Sensors with I<sup>2</sup>C & SPI Interface

#### Introduction

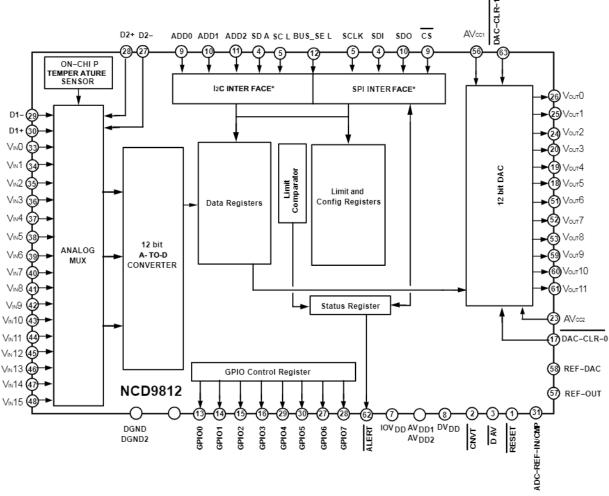

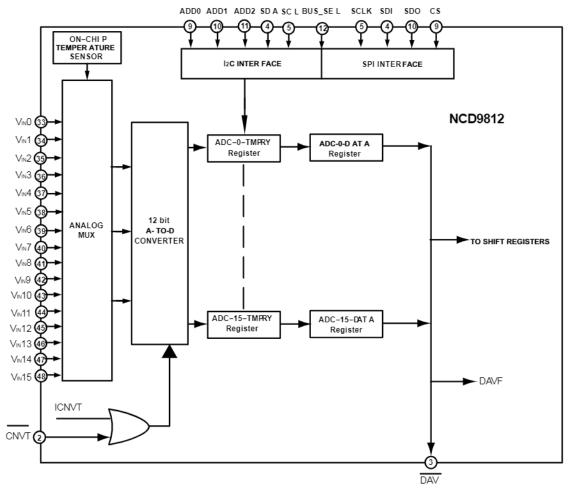

The NCD9812 is a serially programmable voltage and temperature monitor. It can monitor its on chip temperature via its local sensor, and two remotely connected diodes and also voltage, via 16 analog inputs. Four of these analog inputs can be programmed to be differential type inputs. By default, they are all single ended inputs. Multiple 12 bit DACs allow for voltage control on 12 pins. Eight GPIO pins allow digital control and monitoring. An /ALERT output is also available to signal out–of–limit conditions.

Communication with the NCD9812 is accomplished via an I<sup>2</sup>C interface which is compatible with industry standard protocols or a 4 wire SPI interface. Both interfaces are available on this part. Through these interfaces the NCD9812s internal registers may be accessed. These registers allow the user to read the current temperature and input voltages, change the configuration settings, adjust each channels limits and set set the output DAC voltages on each of the 12 channels available.

The NCD9812 is available in a 64-lead QFN package and 64-lead TQFP operates over a temperature range of -40 to +125°C.

#### Features

- On-chip Temperature Sensor (±2.5°C Accuracy)

- 2 Remote Temperature Sensors (±3.5°C Accuracy)

- 16 Analog Voltage Inputs (12 bit).

2 Differential and 12 Single Ended

- 12, 12 bit DAC Output Channels

- 0 V to 5 V

- 8 Digital GPIO Pins

- 2.5 V Internal Reference

- · Power Saving Shutdown Mode

- SPI and I<sup>2</sup>C Interface

- Package Type:

- ♦ 64-lead QFN

- 64-lead TQFP

#### ON Semiconductor®

www.onsemi.com

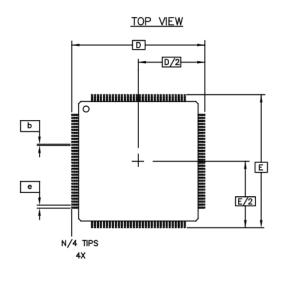

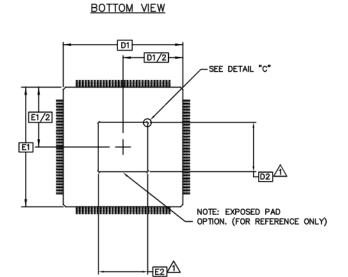

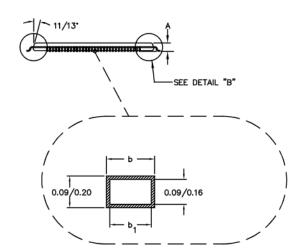

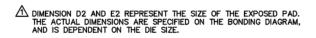

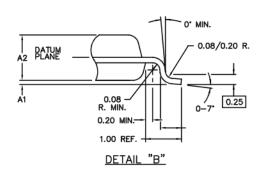

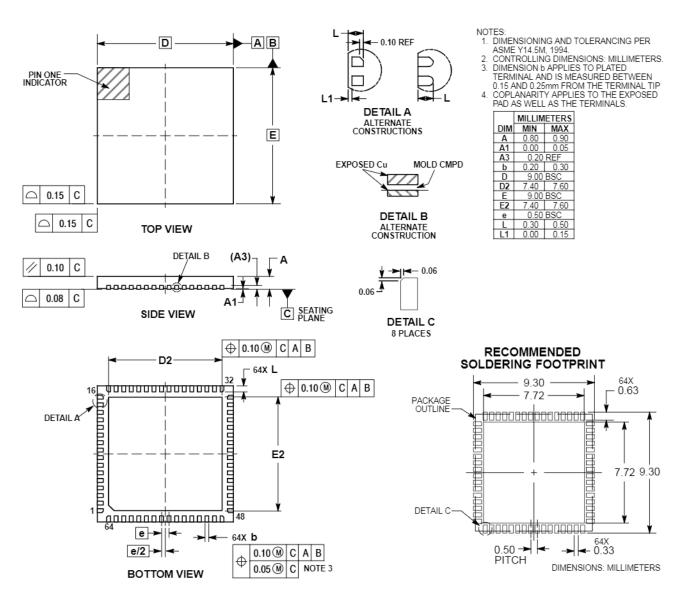

TQFP64 EP, 10x10 CASE 136AC

A = Assembly Location

WL = Wafer Lot YY = Year

WW = Work Week

G = Pb-Free Package

QFN64 9x9, 0.5P CASE 485CT

MARKING

DIAGRAMS

NCD9812

AWLYYWWG

= Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

#### ORDERING INFORMATION

| Device       | Package | Shipping <sup>†</sup> |

|--------------|---------|-----------------------|

| NCD9812FBR2G | TQFP64  | 1000 / Tape & Reel    |

| NCD9812MNTXG | QFN64   | 1000 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

This document, and the information contained herein, is CONFIDENTIAL AND PROPRIETARY and the property of Semiconductor Components Industries, LLC., dba ON Semiconductor. It shall not be used, published, disclosed or disseminated outside of the Company, in whole or in part, without the written permission of ON Semiconductor. Reverse engineering of any or all of the information contained herein is strictly prohibited.

© 2016, SCILLC. All Rights Reserved.

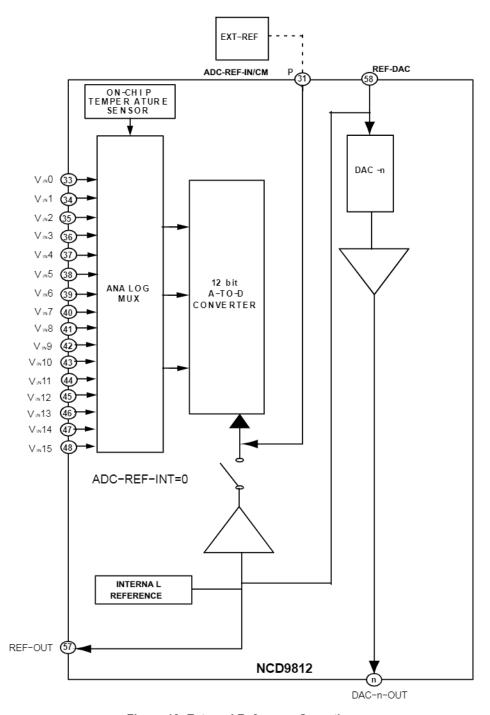

Figure 1. Functional Block Diagram of NCD9812

#### **Pin Connections**

Figure 2. Pin Connections (Top View)

# Table 1. PIN FUNCTION DESCRIPTION

| Pin No. | Pin Name           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | /RESET             | Active low reset input. A hardware reset is performed when a logic low is seen on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2       | /DAV               | Data available. Active low output. In direct mode, this pin goes low when the conversion ends. In auto mode, a 1 µs pulse appears on this pin when the conversion cycle finishes. /DAV stays high when inactive.                                                                                                                                                                                                                                                                                                                                         |

| 3       | /CNVT              | External Conversion Trigger. Active Low. The falling edge starts the sampling and conversion of the ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4       | SDI / SDA          | Serial Data Input in SPI mode. Serial Data Input/Output in I <sup>2</sup> C mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5       | SCLK / SCL         | Serial Clock Input for SPI and I <sup>2</sup> C interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6       | DGND               | Digital Ground. This is the ground pin for all the digital circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7       | IOV <sub>DD</sub>  | Interface supply rail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8       | DV <sub>DD</sub>   | Power Supply. Can be powered from a supply in the range 3V to 5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9       | /CS/ADD0           | Chip Select. Slave transmit enable in SPI mode – active low. Address selection pin for I <sup>2</sup> C mode. Can be tied high or low to give multiple address options.                                                                                                                                                                                                                                                                                                                                                                                  |

| 10      | SDO/ADD1           | Serial Data Out in SPI mode. Address selection pin for I <sup>2</sup> C mode. Can be tied high or low to give multiple address options.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11      | ADD2               | Address selection pin for I <sup>2</sup> C mode. Can be tied high or low to give multiple address options.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12      | BUS_SEL            | Selects I <sup>2</sup> C or SPI interface. BUS_SEL = DGND selects I <sup>2</sup> C; BUS_SEL = V <sub>DD</sub> selects SPI.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13      | GPIO0              | Programmable general purpose digital input or output. Requires pull up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 14      | GPIO1              | Programmable general purpose digital input or output. Requires pull up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15      | GPIO2              | Programmable general purpose digital input or output. Requires pull up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16      | GPIO3              | Programmable general purpose digital input or output. Requires pull up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

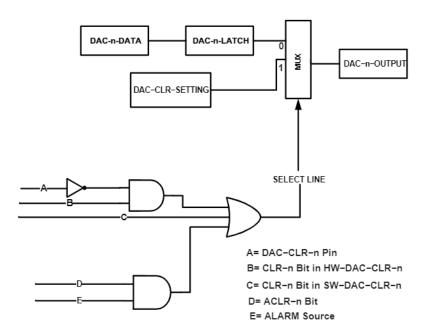

| 17      | /DAC-CLR-0         | DAC clear control signal, digital input, active low. When low, all DACs associated with the DAC-CLR-0 pin enter a clear state, the DAC Latch is loaded with predefined code, and the output is set to the corresponding level. However, the DAC-Data Register does not change. When the DAC goes back to normal operation, the DAC Latch is loaded with the previous data from the DAC-Data Register and the output returns to the previous level, regardless of the status of the SLDAC-n bit. When this pin is high, the DACs are in normal operation. |

| 18      | V <sub>OUT</sub> 5 | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 19      | V <sub>OUT</sub> 4 | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 20      | V <sub>OUT</sub> 3 | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 21      | AGND4              | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 22      | AGND3              | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 23      | AV <sub>CC2</sub>  | Power rail for V <sub>OUT</sub> 0, V <sub>OUT</sub> 1, V <sub>OUT</sub> 2, V <sub>OUT</sub> 3, V <sub>OUT</sub> 4, V <sub>OUT</sub> 5. Must be tied to AV <sub>CC1</sub> .                                                                                                                                                                                                                                                                                                                                                                               |

| 24      | V <sub>OUT</sub> 2 | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 25      | V <sub>OUT</sub> 1 | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 26      | V <sub>OUT</sub> 0 | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 27      | D1-/GPIO6          | Negative Connection to Remote Temperature Sensor. Can be re-configured as a bi-directional GPIO pin (requires pull up resistor).                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 28      | D1+/GPIO7          | Positive Connection to Remote Temperature Sensor. Can be re-configured as a bi-directional GPIO pin (requires pull up resistor).                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 29      | D2-/GPIO4          | Negative Connection to Remote Temperature Sensor. Can be re-configured as a bi-directional GPIO pin (requires pull up resistor).                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 30      | D2+/GPIO5          | Positive Connection to Remote Temperature Sensor. Can be re-configured as a bi-directional GPIO pin (requires pull up resistor).                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 31      | ADC-REF-IN/CMP     | External ADC reference input when external V <sub>REF</sub> is used to drive ADC. Compensation capacitor connection when internal V <sub>REF</sub> is used to drive ADC.                                                                                                                                                                                                                                                                                                                                                                                 |

| 32      | ADC-GND            | ADC ground. Must be connected to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 33      | V <sub>IN</sub> 0  | Analog Input. Programmable as single ended or differential input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 1. PIN FUNCTION DESCRIPTION

| Pin No. | Pin Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34      | V <sub>IN</sub> 1   | Analog Input. Programmable as single ended or differential input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 35      | V <sub>IN</sub> 2   | Analog Input. Programmable as single ended or differential input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 36      | V <sub>IN</sub> 3   | Analog Input. Programmable as single ended or differential input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 37      | V <sub>IN</sub> 4   | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 38      | V <sub>IN</sub> 5   | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 39      | V <sub>IN</sub> 6   | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 40      | V <sub>IN</sub> 7   | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 41      | V <sub>IN</sub> 8   | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 42      | V <sub>IN</sub> 9   | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 43      | V <sub>IN</sub> 10  | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 44      | V <sub>IN</sub> 11  | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 45      | V <sub>IN</sub> 12  | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 46      | V <sub>IN</sub> 13  | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 47      | V <sub>IN</sub> 14  | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 48      | V <sub>IN</sub> 15  | Analog Input. Single Ended input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 49      | AV <sub>DD1</sub>   | Analog Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 50      | AV <sub>DD2</sub>   | Analog Power Supply.(Must be connected to AVDD1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 51      | V <sub>OUT</sub> 6  | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 52      | V <sub>OUT</sub> 7  | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 53      | V <sub>OUT</sub> 8  | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 54      | AGND1               | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 55      | AGND2               | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 56      | AV <sub>CC1</sub>   | Power rail for V <sub>OUT</sub> 6, V <sub>OUT</sub> 7, V <sub>OUT</sub> 8, V <sub>OUT</sub> 9, V <sub>OUT</sub> 10, V <sub>OUT</sub> 11. Must be tied to AV <sub>CC2</sub> .                                                                                                                                                                                                                                                                                                                                                                             |

| 57      | REF-OUT             | Internal Reference Output which is internally shorted with REF-DAC pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 58      | REF-DAC             | DAC reference is internally supplied through ADC internal reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 59      | V <sub>OUT</sub> 9  | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 60      | V <sub>OUT</sub> 10 | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 61      | V <sub>OUT</sub> 11 | Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 62      | /ALERT              | Open-Drain Logic Output Used as Interrupt. Active low output. Pulled low when one or more of the measurement channels are out of range.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 63      | /DAC-CLR-1          | DAC clear control signal, digital input, active low. When low, all DACs associated with the DAC-CLR-1 pin enter a clear state, the DAC Latch is loaded with predefined code, and the output is set to the corresponding level. However, the DAC-Data Register does not change. When the DAC goes back to normal operation, the DAC Latch is loaded with the previous data from the DAC-Data Register and the output returns to the previous level, regardless of the status of the SLDAC-n bit. When this pin is high, the DACs are in normal operation. |

| 64      | DGND2               | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 2. ABSOLUTE MAXIMUM RATINGS

| Rating                                            | Value                             | Units |

|---------------------------------------------------|-----------------------------------|-------|

| AV <sub>DD</sub> to GND                           | -0.3 to +6                        | V     |

| DV <sub>DD</sub> to GND                           | -0.3 to +6                        | V     |

| IOV <sub>DD</sub> to GND                          | -0.3 to +6                        | V     |

| AV <sub>CC</sub> to GND                           | -0.3 to +6                        | V     |

| DV <sub>DD</sub> to DGND                          | -0.3 to +6                        | V     |

| Analog input voltage to GND                       | -0.3 to AV <sub>DD</sub> + 0.3    | V     |

| /ALERT, GPIO0-3. SCLK/SCL, and SDI/SDA to GND     | -0.3 to +6                        | V     |

| D1+/GPIO4, D1-/GPIO5, D2+/GPIO6, D2-/GPIO7 to GND | -0.3 V to AV <sub>DD</sub> + 0.3  | V     |

| Digital input voltage to DGND                     | -0.3 V to IOV <sub>DD</sub> + 0.3 | V     |

| SDO and /DAV to GND                               | -0.3 V to IOV <sub>DD</sub> + 0.3 | V     |

| Operating Temperature Range                       | -40 to +125                       | °C    |

| Storage Temperature Range                         | -40 to 150                        | °C    |

| Junction Temperature Range                        | +150                              | °C    |

| ESD Capability, Human Body Model (Note 2)         | 2500                              | V     |

| ESD Capability, Charged Device Model (Note 2)     | 1000                              | V     |

| ESD Capability, Machine Model (Note 2)            | 150                               | V     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114) ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

#### Table 3. THERMAL CHARACTERISTICS

| Rating                                        | Symbol       | Value | Units |

|-----------------------------------------------|--------------|-------|-------|

| Thermal Characteristics, QFN-64 (Note 3)      |              |       | °C/W  |

| Thermal Resistance, Junction-to-Air (Note 4)  | $R_{0JA}$    | TBD   |       |

| Thermal Reference, Junction-to-Lead2 (Note 4) | $R_{\mu JA}$ | TBD   |       |

- 3. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- As measured using a copper heat spreading area of 650 mm<sup>2</sup> (or 1 in<sup>2</sup>), of 1 oz copper thickness.

# Table 4. ELECTRICAL CHARACTERISTICS

All specifications for  $-40^{\circ}$ C to  $+105^{\circ}$ C, AV<sub>DD</sub> = DV<sub>DD</sub> = 4.5V to 5.5V, AV<sub>CC</sub> = +5V, AGND = DGND = 0V, IOV<sub>DD</sub> = 2.7V to 5.5V, DAC output = 0V to 5V, unless otherwise noted.

| Parameter                                   | Test Conditions                                                                                                    | Min   | Тур    | Max   | Units            |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------|--------|-------|------------------|

| DAC Performance                             |                                                                                                                    |       |        |       |                  |

| DAC DC Accuracy                             |                                                                                                                    |       |        |       |                  |

| Resolution                                  | Guaranteed by design                                                                                               | 12    |        |       | Bits             |

| INL (Relative Accuracy)                     | Measured by line passing through codes 020h and FFFh. $T_A = 25^{\circ}C$                                          |       |        | ±5    | LSB              |

| DNL (Differential Nonlinearity)             | 12-bit monotonic, measured by line passing through codes 020h and FFFh                                             |       | ±0.3   | ±5    | LSB              |

| TUE (Total Unadjusted Error)                | T <sub>A</sub> = +25°C, DAC output = 5.0V                                                                          |       |        | ±10   | mV               |

|                                             | T <sub>A</sub> = +25°C, DAC output = 12.5V                                                                         |       |        | ±30   | mV               |

| Offset error                                | T <sub>A</sub> = +25°C, DAC output = 5.0V code 020h                                                                |       |        | ±5    | mV               |

|                                             | T <sub>A</sub> = +25°C, DAC output = 12.5V code 020h                                                               |       |        | ±10   | mV               |

| Offset error temperature coefficient        |                                                                                                                    |       | ±1     |       | ppm/°C           |

| Gain error                                  | External reference, output = 0 V to +5 V T <sub>A</sub> = 25°C                                                     |       | ±0.025 | ±0.15 | %FSR             |

| Gain temperature coefficient                |                                                                                                                    |       | ±2     |       | ppm/°C           |

| DAC Output Characteristics                  |                                                                                                                    |       |        |       | 1                |

| Output voltage range                        | V <sub>REF</sub> = 2.5V, gain = 2                                                                                  | 0     |        | 5     | V                |

| Output voltage settling time                | DAC output = 0V to +5V, code 400h to code C00h, to 1/2 LSB, from /CS rising edge, $R_L = 2k\Omega$ , $C_L = 200pF$ |       | 10     |       | μS               |

| Slew rate                                   |                                                                                                                    |       | 2.3    |       | V/µs             |

| Short-circuit current                       | Full-scale current shorted to ground                                                                               |       | 30     |       | mA               |

| Load current                                | Source and/or sink within 200mV of supply                                                                          |       | ±10    |       | mA               |

| Capacitive load stability                   | R <sub>L</sub> = ∞                                                                                                 | 50    |        |       | nF               |

| DC output impedance                         | Code 800h                                                                                                          |       | 10     |       | Ω                |

| Power-on overshoot                          | AV <sub>CC</sub> 0 to 5V, 2ms ramp                                                                                 |       | 5      |       | mV               |

| Digital-to-analog glitch energy             | Code changes from 7FFh to 800h, 800h to 7FFh                                                                       |       | 18     |       | nV-s             |

| Digital feedthrough                         | Device is not accessed                                                                                             |       | 0.15   |       | nV-s             |

| Output noise                                | T <sub>A</sub> = +25°C, at 1kHz, code 800h, gain = 2, excludes reference                                           |       | 93     |       | nV/√Hz           |

|                                             | F = 0.1Hz to 10Hz, excludes reference                                                                              |       | 61     |       | μV <sub>PP</sub> |

| Internal Reference                          |                                                                                                                    |       |        |       |                  |

| Output voltage                              | T <sub>A</sub> = +25°C, REF-OUT pin                                                                                | 2.495 | 2.5    | 2.505 | V                |

| Output Impedance                            |                                                                                                                    |       | 600    |       | Ω                |

| Reference temperature coefficient           |                                                                                                                    |       | 10     | 25    | ppm/°C           |

| ADC Performance                             |                                                                                                                    |       |        |       | 1                |

| ADC DC Accuracy (for AV <sub>DD</sub> = 5V) |                                                                                                                    |       |        |       |                  |

| Resolution                                  | Guaranteed by design                                                                                               |       | 12     |       | Bits             |

| INL (Integral nonlinearity)                 |                                                                                                                    |       | ±0.5   | ±1    | LSB              |

| DNL (Differential nonlinearity)             |                                                                                                                    |       | ±0.5   | ±1    | LSB              |

| Single Ended Mode                           | 1                                                                                                                  |       |        |       | 1                |

| Offset error                                |                                                                                                                    |       | ±1     | ±5    | LSB              |

# Table 4. ELECTRICAL CHARACTERISTICS

All specifications for  $-40^{\circ}$ C to  $+105^{\circ}$ C,  $AV_{DD} = DV_{DD} = 4.5$ V to 5.5V,  $AV_{CC} = +5$ V, AGND = DGND = 0V,  $IOV_{DD} = 2.7$ V to 5.5V, DAC output = 0V to 5V, unless otherwise noted.

| Parameter                     | Test Conditions                                                                             | Min                 | Тур   | Max                    | Units |

|-------------------------------|---------------------------------------------------------------------------------------------|---------------------|-------|------------------------|-------|

| Offset error match            |                                                                                             |                     | ±1    |                        | LSB   |

| Gain error                    | External reference                                                                          |                     | ±3.5  | ±7.5                   | LSB   |

| Gain error match              |                                                                                             |                     | ±2    |                        | LSB   |

| Differential Mode             | ·                                                                                           |                     |       |                        |       |

| Gain error                    | External reference, 0V to $(2xV_{REF})$ mode, $V_{CM} = 2.5V$                               |                     | ±3    | ±13                    | LSB   |

|                               | External reference, 0V to V <sub>REF</sub> mode, V <sub>CM</sub> = 1.25V                    |                     | ±3    | ±11                    | LSB   |

| Gain error match              |                                                                                             |                     | ±3    |                        | LSB   |

| Zero code error               | 0V to (2xV <sub>REF</sub> ) mode, V <sub>CM</sub> = 2.5V                                    |                     | ±1    | ±3                     | LSB   |

|                               | External reference, 0V to V <sub>REF</sub> mode,<br>V <sub>CM</sub> = 1.25V                 |                     | ±1    | ±3                     | LSB   |

| Zero code error match         |                                                                                             |                     | ±1.5  |                        | LSB   |

| Common mode rejection         | DC, 0V to (2xV <sub>REF</sub> ) mode                                                        |                     | 67    |                        | dB    |

| Sampling Dynamics             |                                                                                             |                     |       |                        |       |

| Conversion rate               | External single analog channel, auto mode                                                   |                     | 500   |                        | kSPS  |

|                               | External single analog channel, direct mode                                                 |                     | 167   |                        | kSPS  |

| Conversioin time              | External single analog channel                                                              |                     | 2     |                        | μS    |

| Autocycle update rate         | All 16 single ended inputs enabled                                                          |                     | 32    |                        | μS    |

| Throughput rate               | SPI clock 12 MHz or greater, single analog channel                                          |                     |       | 500                    | kSPS  |

| Analog Input                  | <u>'</u>                                                                                    | '                   |       |                        |       |

| Full scale input voltage      | Single ended, 0V to V <sub>REF</sub> mode                                                   | 0                   |       | V <sub>REF</sub>       | V     |

|                               | Single ended, 0V to (2xV <sub>REF</sub> ) mode                                              | 0                   |       | 2xV <sub>REF</sub>     | V     |

|                               | $V_{\text{IN+}}$ – $V_{\text{IN-}},$ fully differential, 0V to $V_{\text{REF}}$ mode        | -V <sub>REF</sub>   |       | +V <sub>REF</sub>      | V     |

|                               | $V_{\text{IN+}}$ – $V_{\text{IN-}}$ , fully differential, 0V to (2x $V_{\text{REF}}$ ) mode | −2xV <sub>REF</sub> |       | +2xV <sub>REF</sub>    | V     |

| Absolute input voltage        | 0V to V <sub>REF</sub> mode                                                                 | GND - 0.2           |       | AV <sub>DD</sub> + 0.2 | V     |

| Input capacitance             |                                                                                             |                     | 40    |                        | pF    |

| DC input leakage current      | Unselected ADC input                                                                        |                     |       | ±10                    | μА    |

| ADC Reference Input           |                                                                                             |                     |       |                        |       |

| Reference input voltage range |                                                                                             | 1.2                 |       | AV <sub>DD</sub>       | V     |

| Input current                 | V <sub>REF</sub> = 2.5V                                                                     |                     | 10    |                        | μА    |

| Internal ADC Reference Buffer | •                                                                                           |                     |       |                        |       |

| Offset                        | T <sub>A</sub> = +25°C                                                                      |                     |       | ±5                     | mV    |

| Internal Temperature Sensor   | •                                                                                           |                     |       | 1                      |       |

| Operating range               |                                                                                             | -40                 |       | +125                   | °C    |

| Accuracy                      | AV <sub>DD</sub> = 5V, T <sub>A</sub> = -40°C to +125°C                                     |                     | ±1.25 | ±2.5                   | °C    |

|                               | AV <sub>DD</sub> = 5V, T <sub>A</sub> = 0°C to +100°C                                       |                     |       | ±1.5                   | °C    |

| Resolution                    | Per LSB, Guaranteed by design                                                               |                     | 0.125 |                        | °C    |

| Conversion rate               | External temperature sensors are disabled                                                   |                     | 15    |                        | ms    |

Table 4. ELECTRICAL CHARACTERISTICS

All specifications for  $-40^{\circ}$ C to  $+105^{\circ}$ C, AV<sub>DD</sub> = DV<sub>DD</sub> = 4.5V to 5.5V, AV<sub>CC</sub> = +5V, AGND = DGND = 0V, IOV<sub>DD</sub> = 2.7V to 5.5V, DAC output = 0V to 5V, unless otherwise noted.

| Parameter                              | Test Conditions                                                                                    | Min  | Тур   | Max                        | Units |

|----------------------------------------|----------------------------------------------------------------------------------------------------|------|-------|----------------------------|-------|

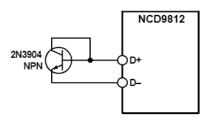

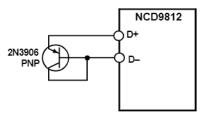

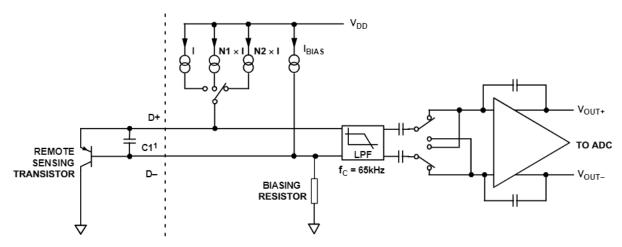

| External Temperature Sensor (using     | 2N3906 external transistor)                                                                        |      |       |                            |       |

| Operating range                        |                                                                                                    | -40  |       | +150                       | °C    |

| Accuracy                               | $AV_{DD} = 5V$ , $T_A = 0$ °C to +100°C,<br>$T_D = -40$ °C to +150°C                               |      |       | ±2                         | °C    |

|                                        | $AV_{DD} = 5V$ , $T_A = -40^{\circ}C$ to $+100^{\circ}C$ , $T_D = -40^{\circ}C$ to $+150^{\circ}C$ |      |       | ±3.5                       | °C    |

| Resolution                             | Per LSB, Guaranteed by design                                                                      |      | 0.125 |                            | °C    |

| Conversion rate per sensor             | With resistance cancellation (RC=1)                                                                | 72   | 93    | 100                        | ms    |

|                                        | With resistance cancellation (RC=0)                                                                | 33   | 44    | 47                         | ms    |

| Digital Logic: /ALERT, /CS, ADD and    | GPIO                                                                                               |      |       |                            |       |

| V <sub>IH</sub> (Input high voltage)   | IOV <sub>DD</sub> = +5V                                                                            | 2.1  |       | 0.3 +<br>IOV <sub>DD</sub> | V     |

|                                        | IOV <sub>DD</sub> = +3.3V                                                                          | 2.1  |       | 0.3 +<br>IOV <sub>DD</sub> | ٧     |

| V <sub>IL</sub> (Input low voltage)    | IOV <sub>DD</sub> = +5V/3.3V, all other pins                                                       | -0.3 |       | 0.8                        | V     |

|                                        | IOV <sub>DD</sub> = +5V/3.3V, <del>CS</del> pin only                                               | -0.3 |       | 0.6                        | V     |

| V <sub>OL</sub> (Output low voltage)   | IOV <sub>DD</sub> = +5V, sinking 5 mA                                                              |      |       | 0.8                        | V     |

|                                        | IOV <sub>DD</sub> = +3.3V, sinking 2 mA                                                            |      |       | 0.8                        | V     |

| High impedance leakage                 |                                                                                                    |      |       | 7                          | μA    |

| High impedance output capacitance      |                                                                                                    |      |       | 10                         | pF    |

| Digital Logic: All except SCL, SDA, // | ALERT, /CS, ADD and GPIO                                                                           |      |       | •                          |       |

| V <sub>IH</sub> (Input high voltage)   | IOV <sub>DD</sub> = +5V                                                                            | 2.3  |       | 0.3 +<br>IOV <sub>DD</sub> | ٧     |

|                                        | IOV <sub>DD</sub> = +3.3V                                                                          | 2.3  |       | 0.3 +<br>IOV <sub>DD</sub> | V     |

| V <sub>IL</sub> (Input low voltage)    | IOV <sub>DD</sub> = +5V                                                                            | -0.3 |       | 0.8                        | V     |

|                                        | IOV <sub>DD</sub> = +3.3V                                                                          | -0.3 |       | 0.8                        | V     |

| Input current                          |                                                                                                    |      |       | ±1                         | μА    |

| Input capacitance                      |                                                                                                    |      |       | 5                          | pF    |

| V <sub>OH</sub> (Output high voltage)  | IOV <sub>DD</sub> = +5V, sourcing 3 mA                                                             | 4.8  |       |                            | V     |

|                                        | IOV <sub>DD</sub> = +3.3V, sourcing 3 mA                                                           | 2.9  |       |                            | V     |

| V <sub>OL</sub> (Output low voltage)   | IOV <sub>DD</sub> = +5V, sinking 3 mA                                                              |      |       | 0.4                        | V     |

|                                        | IOV <sub>DD</sub> = +3.3V, sinking 3 mA                                                            |      |       | 0.4                        | V     |

| High impedance leakage                 |                                                                                                    |      |       | ±5                         | μΑ    |

| High impedance output capacitance      |                                                                                                    |      |       | 10                         | pF    |

| Digital Logic: SDA, SCL                |                                                                                                    |      |       |                            |       |

| V <sub>IH</sub> (Input high voltage)   | IOV <sub>DD</sub> = +5V                                                                            | 2.1  |       | 0.3 +<br>IOV <sub>DD</sub> | ٧     |

|                                        | IOV <sub>DD</sub> = +3.3V                                                                          | 2.1  |       | 0.3 +<br>IOV <sub>DD</sub> | V     |

| V <sub>IL</sub> (Input low voltage)    | IOV <sub>DD</sub> = +5V                                                                            | -0.3 |       | 0.8                        | V     |

|                                        | IOV <sub>DD</sub> = +3.3V                                                                          | -0.3 |       | 0.8                        | V     |

# Table 4. ELECTRICAL CHARACTERISTICS

All specifications for  $-40^{\circ}$ C to  $+105^{\circ}$ C,  $AV_{DD} = DV_{DD} = 4.5$ V to 5.5V,  $AV_{CC} = +5$ V, AGND = DGND = 0V,  $IOV_{DD} = 2.7$ V to 5.5V, DAC output = 0V to 5V, unless otherwise noted.

| Parameter                            | Test Conditions                                                                       | Min  | Тур | Max  | Units |

|--------------------------------------|---------------------------------------------------------------------------------------|------|-----|------|-------|

| Input current                        |                                                                                       |      |     | ±5   | μA    |

| Input capacitance                    |                                                                                       |      |     | 5    | pF    |

| V <sub>OL</sub> (Output low voltage) | IOV <sub>DD</sub> = +5V, sinking 3mA                                                  | 0    |     | 0.4  | V     |

|                                      | IOV <sub>DD</sub> = +3.3V, sinking 3mA                                                | 0    |     | 0.4  | V     |

| High impedance leakage               |                                                                                       |      |     | ±5   | μА    |

| High impedance output capacitance    |                                                                                       |      |     | 10   | pF    |

| Power on delay                       | From AV <sub>DD</sub> , DV <sub>DD</sub> ≥ 2.7V and AV <sub>CC</sub> ≥ 4.5V           |      | 100 | 250  | μs    |

| Power down recovery time             | From /CS rising time                                                                  |      |     | 70   | μS    |

| Convert pulse width                  |                                                                                       | 20   |     |      | ns    |

| Reset pulse width                    |                                                                                       | 20   |     |      | ns    |

| POWER REQUIREMENTS                   |                                                                                       |      |     |      |       |

| AV <sub>DD</sub>                     | AV <sub>DD</sub> must be ≥ (V <sub>REF</sub> + 1.2V)                                  | +2.7 |     | +5.5 | V     |

| Al <sub>DD</sub>                     | AV <sub>DD</sub> and DV <sub>DD</sub> combined, normal operation, no DAC load         |      | 7.9 | 12.5 | mA    |

|                                      | AV <sub>DD</sub> and DV <sub>DD</sub> combined, all blocks in power down              |      | 2.8 |      | mA    |

| AV <sub>CC</sub>                     |                                                                                       | +4.5 |     | +5.5 | V     |

| Al <sub>CC</sub>                     | AV <sub>CC</sub> , no load, DACs at code 800h                                         |      |     | 7.5  | mA    |

| Power dissipation                    | Normal operation, AV <sub>DD</sub> = DV <sub>DD</sub> = 5V,<br>AV <sub>CC</sub> = 15V |      | 50  | 120  | mW    |

| DV <sub>DD</sub>                     |                                                                                       | +2.7 |     | +5.5 | V     |

| IOV <sub>DD</sub>                    |                                                                                       | +2.7 |     | +5.5 | V     |

| GENERAL INTERFACE INFORMATION        |                                                                                       |      |     |      |       |

| Bit Rate                             | SPI                                                                                   |      |     | 20   | MHz   |

|                                      | I <sup>2</sup> C Standard Mode                                                        |      |     | 100  | kHz   |

|                                      | I <sup>2</sup> C Fast Mode                                                            |      |     | 400  | kHz   |

|                                      | I <sup>2</sup> C High Speed Mode                                                      |      |     | 3.4  | MHz   |

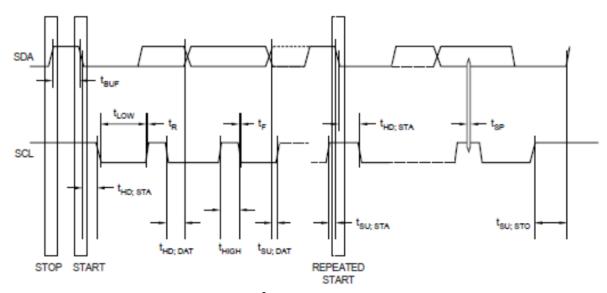

# I<sup>2</sup>C TIMING SPECIFICATION

### Table 5. I<sup>2</sup>C TIMING CHARACTERISTICS PARAMETERS

$T_A = -40$ °C to +125°C,  $V_{DD} = 3.3$  V unless otherwise noted.

| Parameter <sup>1</sup>                  | Symbol              | Conditions                                                              | Min                              | Max                      | Units                    |

|-----------------------------------------|---------------------|-------------------------------------------------------------------------|----------------------------------|--------------------------|--------------------------|

| Clock Frequency                         | fscL                | Standard Mode Fast Mode High speed Mode (100pF) High speed Mode (400pF) | 10                               | 100<br>400<br>3.4<br>1.7 | kHz<br>kHz<br>MHz<br>MHz |

| Bus Free Time                           | t <sub>BUF</sub>    | Standard Mode<br>Fast Mode                                              | 4.7<br>1.3                       |                          | s<br>µs                  |

| Start Hold Time <sup>2</sup>            | t <sub>HD;STA</sub> | Standard Mode<br>Fast Mode<br>High speed Mode                           | 4.0<br>600<br>160                |                          | μs<br>ns<br>ns           |

| SCL Low Time                            | t <sub>LOW</sub>    | Standard Mode Fast Mode High speed Mode (100pF) High speed Mode (400pF) | 4.7<br>1.3<br>160<br>320         |                          | μs<br>μs<br>ns<br>ns     |

| SCL High Time                           | t <sub>HIGH</sub>   | Standard Mode Fast Mode High speed Mode (100pF) High speed Mode (400pF) | 4.0<br>600<br>60<br>120          |                          | μs<br>ns<br>ns<br>ns     |

| Start Setup Time                        | t <sub>SU;STA</sub> | Standard Mode<br>Fast Mode<br>High speed Mode                           | 4.7<br>600<br>160                |                          | μs<br>ns<br>ns           |

| Data Setup Time <sup>3</sup>            | t <sub>SU;DAT</sub> | Standard Mode<br>Fast Mode<br>High speed Mode                           | 250<br>100<br>10                 | 250<br>100<br>10         | ns                       |

| Data Hold Time <sup>4</sup>             | t <sub>HD;DAT</sub> | Standard Mode Fast Mode High speed Mode (100pF) High speed Mode (400pF) | 0<br>0<br>0                      | 3.45<br>0.9<br>70<br>150 | μs<br>μs<br>ns<br>ns     |

| SCL Rise Time                           | trcL                | Standard Mode Fast Mode High speed Mode (100pF) High speed Mode (400pF) | 20+0.1C <sub>B</sub><br>10<br>20 | 1000<br>300<br>40<br>80  | ns<br>ns<br>ns           |

| SCL Rise Time<br>(after repeated start) | t <sub>RCL1</sub>   | Standard Mode Fast Mode High speed Mode (100pF) High speed Mode (400pF) | 20+0.1C <sub>B</sub><br>10<br>20 | 1000<br>300<br>80<br>160 | ns<br>ns<br>ns<br>ns     |

| SCL Fall Time                           | t <sub>FCL</sub>    | Standard Mode Fast Mode High speed Mode (100pF) High speed Mode (400pF) | 20+0.1C <sub>B</sub><br>10<br>20 | 300<br>300<br>40<br>80   | ns<br>ns<br>ns           |

| SDA Rise Time                           | t <sub>RDA</sub>    | Standard Mode Fast Mode High speed Mode (100pF) High speed Mode (400pF) | 20+0.1C <sub>B</sub><br>10<br>20 | 1000<br>300<br>80<br>160 | ns<br>ns<br>ns           |

Guaranteed by design, but not production tested.

Time from 10% of SDA to 90% of SCL.

<sup>3.</sup> Time for 10% or 90% of SDA to 10% of SCL.

<sup>4.</sup> A device must internally provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL.

### Table 5. I<sup>2</sup>C TIMING CHARACTERISTICS PARAMETERS

$T_A = -40$ °C to +125°C,  $V_{DD} = 3.3$  V unless otherwise noted.

| Parameter <sup>1</sup>     | Symbol              | Conditions                                      | Min                  | Max              | Units          |

|----------------------------|---------------------|-------------------------------------------------|----------------------|------------------|----------------|

| SDA Fall Time              | t <sub>FDA</sub>    | Standard Mode Fast Mode High speed Mode (100pF) | 20+0.1C <sub>B</sub> | 300<br>300<br>80 | ns<br>ns<br>ns |

|                            |                     | High speed Mode (400pF)                         | 20                   | 160              | ns             |

| Stop Setup Time            | t <sub>SU;STO</sub> | Standard Mode<br>Fast Mode<br>High speed Mode   | 4.0<br>600<br>160    |                  | μs<br>ns<br>ns |

| Capacitive load            | C <sub>B</sub>      |                                                 |                      | 400              | pF             |

| Glitch Immunity            | t <sub>SP</sub>     | Fast Mode<br>High-speed Mode                    |                      | 50<br>10         | ns<br>ns       |

| Noise margin at high level | V <sub>NH</sub>     | Standard Mode<br>Fast Mode<br>High speed Mode   | 0.2V <sub>DD</sub>   |                  | ٧              |

| Noise margin at low level  | V <sub>NL</sub>     | Standard Mode<br>Fast Mode<br>High speed Mode   | 0.1V <sub>DD</sub>   |                  | ٧              |

- Guaranteed by design, but not production tested.

Time from 10% of SDA to 90% of SCL.

- 3. Time for 10% or 90% of SDA to 10% of SCL.

- 4. A device must internally provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL.

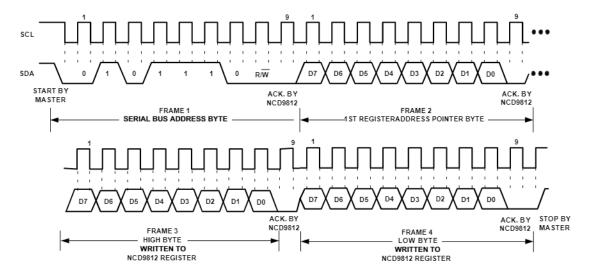

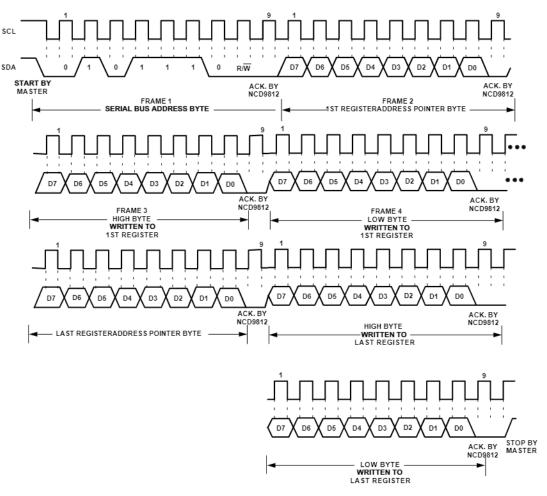

Figure 3. I<sup>2</sup>C Serial Interface Timing

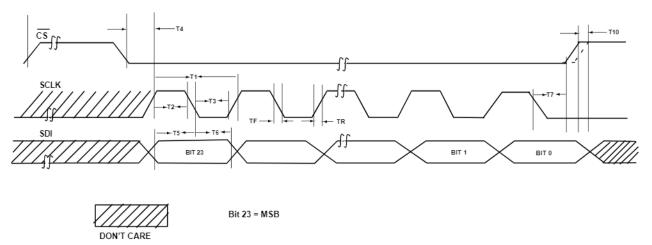

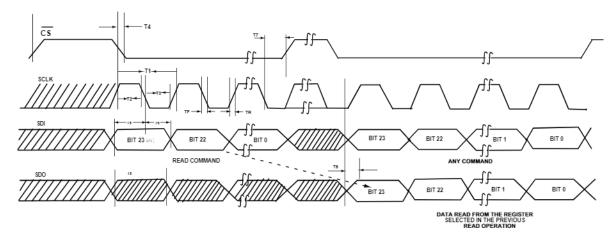

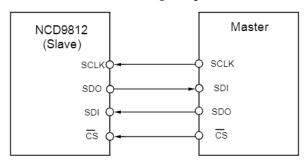

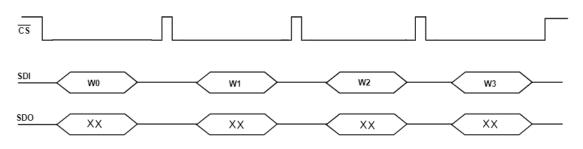

# SPI TIMING SPECIFICATION

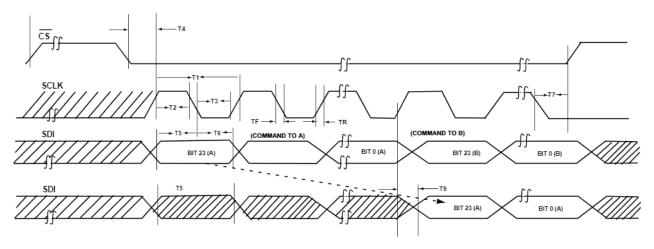

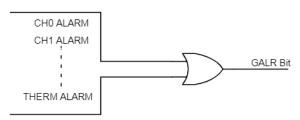

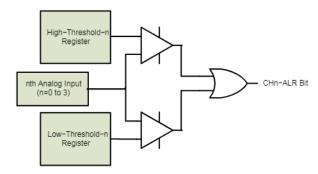

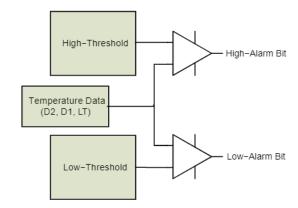

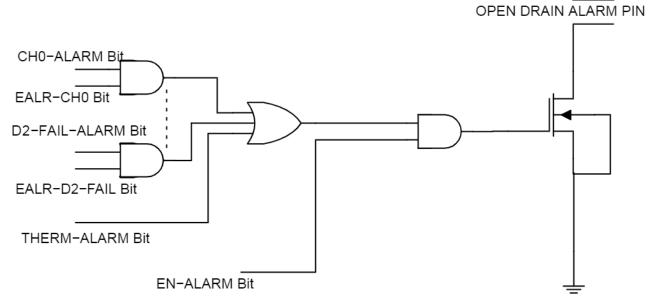

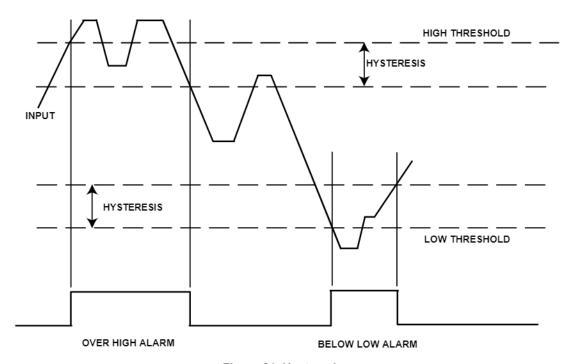

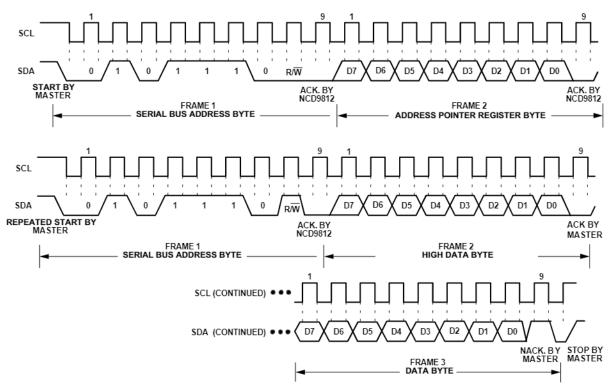

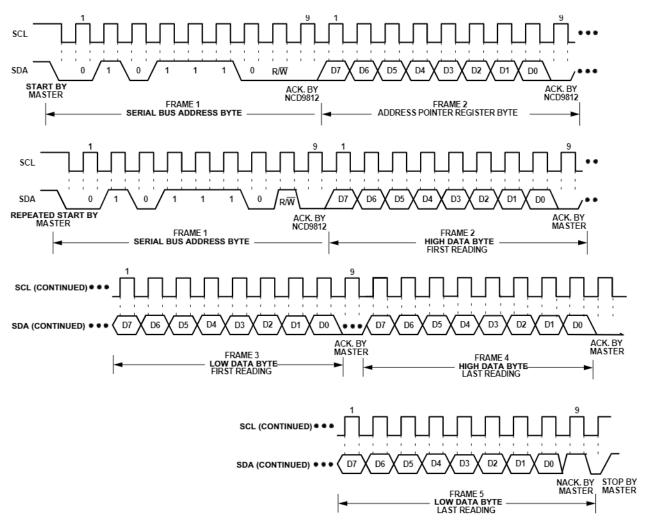

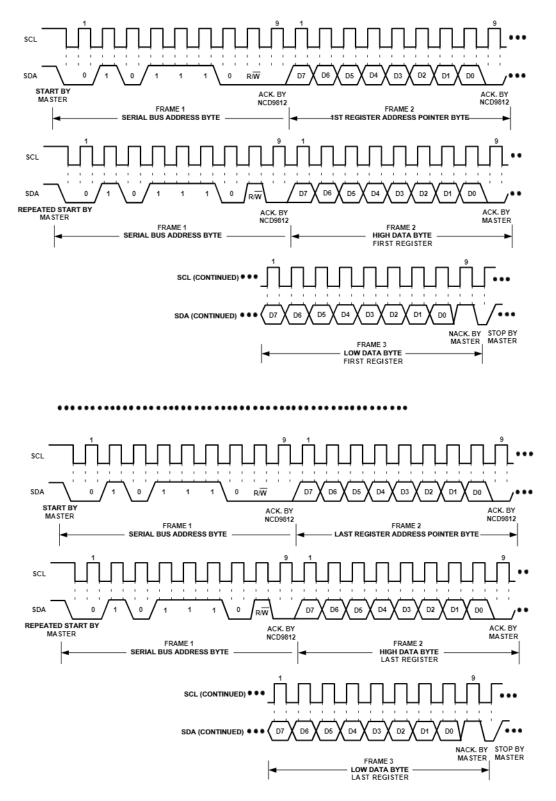

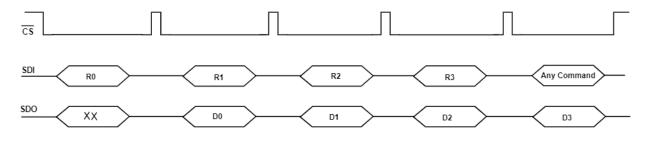

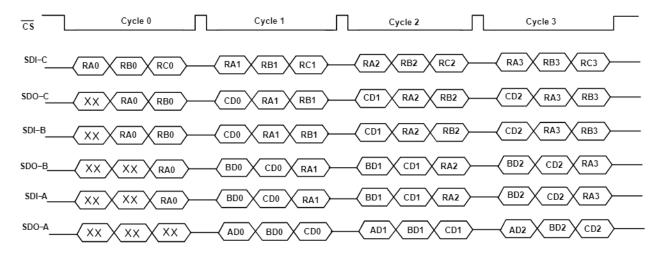

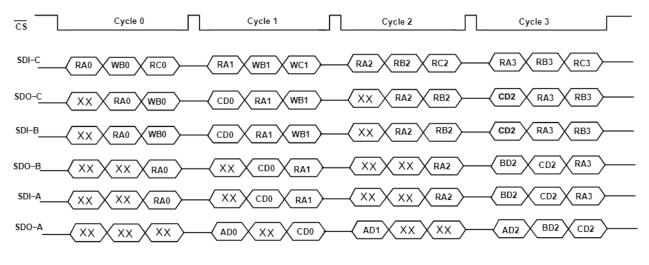

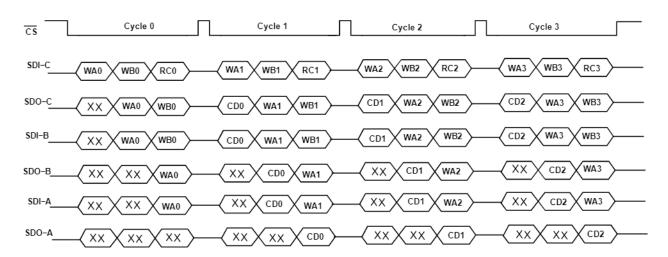

Table 6. SPI TIMING CHARACTERISTICS PARAMETERS