# N-Channel 650V (D-S) MOSFET

| PRODUCT SUMMARY                       |                 |      |  |  |

|---------------------------------------|-----------------|------|--|--|

| $V_{DS}$ (V) at $T_J$ max.            | 650             |      |  |  |

| R <sub>DS(on)</sub> max. (Ω) at 25 °C | $V_{GS} = 10 V$ | 0.50 |  |  |

| Q <sub>g</sub> max. (nC)              | 71              |      |  |  |

| Q <sub>gs</sub> (nC)                  | 14              |      |  |  |

| Q <sub>gd</sub> (nC)                  | 33              |      |  |  |

| Configuration                         | Single          |      |  |  |

#### **FEATURES**

- Reduced t<sub>rr</sub>, Q<sub>rr</sub>, and I<sub>RRM</sub>

- Low figure-of-merit (FOM) Ron x Qg

- Low input capacitance (Ciss)

- Low switching losses due to reduced Q<sub>rr</sub>

- Ultra low gate charge (Q<sub>q</sub>)

- Avalanche energy rated (UIS)

| ABSOLUTE MAXIMUM RATINGS (T <sub>C</sub> :                | = 25 °C, unless otherw                                         | vise noted)     |       |       |  |

|-----------------------------------------------------------|----------------------------------------------------------------|-----------------|-------|-------|--|

| PARAMETER                                                 |                                                                | SYMBOL          | LIMIT | UNIT  |  |

| Drain-Source Voltage                                      |                                                                | V <sub>DS</sub> | 650   | v     |  |

| Gate-Source Voltage                                       |                                                                | V <sub>GS</sub> | ± 30  |       |  |

| Continuous Drain Current (T <sub>.I</sub> = 150 °C)       | $V_{GS}$ at 10 V $T_C = 25 \degree C$<br>$T_C = 100 \degree C$ |                 | 18    |       |  |

| Continuous Drain Current (1) = 150°C)                     | $V_{GS}$ at 10 V $T_C = 100 \text{ °C}$                        | I <sub>D</sub>  | 16    | А     |  |

| Pulsed Drain Current <sup>a</sup>                         |                                                                | I <sub>DM</sub> | 53    |       |  |

| Linear Derating Factor                                    |                                                                |                 | 1.7   | W/°C  |  |

| Single Pulse Avalanche Energy <sup>b</sup>                |                                                                | E <sub>AS</sub> | 367   | mJ    |  |

| Maximum Power Dissipation                                 | PD                                                             | 68              | W     |       |  |

| Operating Junction and Storage Temperature Range          | T <sub>J</sub> , T <sub>stg</sub>                              | -55 to +150     | °C    |       |  |

| Drain-Source Voltage Slope $T_J = 125 \text{ °C}$         |                                                                | dV/dt           | 37    | V/ns  |  |

| Reverse Diode dV/dt <sup>d</sup>                          |                                                                | uv/di           | 31    | v/115 |  |

| Soldering Recommendations (Peak Temperature) <sup>c</sup> | for 10 s                                                       |                 | 300   | °C    |  |

#### Notes

a. Repetitive rating; pulse width limited by maximum junction temperature. b.  $V_{DD} = 50$  V, starting T<sub>J</sub> = 25 °C, L = 28.2 mH, R<sub>g</sub> = 25  $\Omega$ , I<sub>AS</sub> = 5.1 A.

c. 1.6 mm from case. d.  $I_{SD} \le I_D$ , dl/dt = 100 A/µs, starting  $T_J = 25$  °C.

| PARAMETER                                                  | SYMBOL                 | TYP.                                                                 |                                        | MAX.                      |      | UNIT |       |      |

|------------------------------------------------------------|------------------------|----------------------------------------------------------------------|----------------------------------------|---------------------------|------|------|-------|------|

| Maximum Junction-to-Ambient                                | R <sub>thJA</sub>      | -                                                                    |                                        | 62                        |      |      |       |      |

| Maximum Junction-to-Case (Drain)                           | R <sub>thJC</sub>      | -                                                                    |                                        | 0.5                       |      |      | °C/W  |      |

|                                                            |                        |                                                                      |                                        |                           |      |      |       |      |

| SPECIFICATIONS (T <sub>J</sub> = 25 °C, u                  | nless otherw           | ise noted)                                                           |                                        |                           |      |      |       |      |

| PARAMETER                                                  | SYMBOL                 |                                                                      |                                        | DNS                       | MIN. | TYP. | MAX.  | UNI  |

| Static                                                     |                        | •                                                                    |                                        |                           |      |      |       |      |

| Drain-Source Breakdown Voltage                             | V <sub>DS</sub>        | V <sub>GS</sub> :                                                    | = 0 V, I <sub>D</sub> = 2              | 50 µA                     | 650  | -    | -     | V    |

| V <sub>DS</sub> Temperature Coefficient                    | $\Delta V_{DS}/T_{J}$  | Referenc                                                             | e to 25 °C, I                          | <sub>0</sub> = 1 mA       | -    | 0.67 | -     | V/°0 |

| Gate-Source Threshold Voltage (N)                          | V <sub>GS(th)</sub>    | V <sub>DS</sub> =                                                    | = V <sub>GS</sub> , I <sub>D</sub> = 2 | 50 µA                     | 2.5  | -    | 4.5   | V    |

| Orte Orimen Laskans                                        |                        |                                                                      | $V_{GS} = \pm 20$ V                    | /                         | -    | -    | ± 100 | nA   |

| Gate-Source Leakage                                        | I <sub>GSS</sub>       |                                                                      | $V_{GS} = \pm 30$ V                    | /                         | -    | -    | ± 1   | μA   |

| Zara Cata Valtaga Drain Current                            | I                      | V <sub>DS</sub> =                                                    | = 650 V, V <sub>GS</sub>               | = 0 V                     | -    | -    | 1     |      |

| Zero Gate Voltage Drain Current                            | IDSS                   | V <sub>DS</sub> = 520 \                                              | /, V <sub>GS</sub> = 0 V,              | T <sub>J</sub> = 125 °C   | -    | -    | 500   | μA   |

| Drain-Source On-State Resistance                           | R <sub>DS(on)</sub>    | $V_{GS} = 10 V$                                                      | I <sub>D</sub>                         | = 11 A                    | -    | 0.36 | -     | Ω    |

| Forward Transconductance                                   | <b>g</b> <sub>fs</sub> | V <sub>DS</sub>                                                      | = 30 V, I <sub>D</sub> =               | 11 A                      | -    | 7.0  | -     | S    |

| Dynamic                                                    |                        | •                                                                    |                                        |                           | •    | •    | •     | •    |

| Input Capacitance                                          | C <sub>iss</sub>       |                                                                      | V <sub>GS</sub> = 0 V,                 |                           | -    | 3322 | -     |      |

| Output Capacitance                                         | C <sub>oss</sub>       |                                                                      | $V_{GS} = 0 V,$<br>$V_{DS} = 100 V,$   |                           | -    | 205  |       | 1    |

| Reverse Transfer Capacitance                               | C <sub>rss</sub>       |                                                                      | f = 1 MHz                              |                           | -    | 120  | -     |      |

| Effective Output Capacitance, Energy Related <sup>a</sup>  | C <sub>o(er)</sub>     |                                                                      |                                        |                           | -    | 84   | -     | pF   |

| Effective Output Capacitance, Time<br>Related <sup>b</sup> | C <sub>o(tr)</sub>     | $V_{DS} = 0 V \text{ to } 520 V, V_{GS} = 0 V$                       |                                        | -                         | 293  | -    | 1     |      |

| Total Gate Charge                                          | Qg                     |                                                                      |                                        |                           | -    | 71   | -     | nC   |

| Gate-Source Charge                                         | Q <sub>gs</sub>        | $V_{GS} = 10 V$                                                      | I <sub>D</sub> = 11 A                  | , V <sub>DS</sub> = 520 V | -    | 14   | -     |      |

| Gate-Drain Charge                                          | Q <sub>gd</sub>        |                                                                      |                                        |                           | -    | 33   | -     |      |

| Turn-On Delay Time                                         | t <sub>d(on)</sub>     |                                                                      | •                                      |                           | -    | 22   | 44    |      |

| Rise Time                                                  | t <sub>r</sub>         |                                                                      | = 520 V, I <sub>D</sub> =              | 11 A,                     | -    | 34   | 68    |      |

| Turn-Off Delay Time                                        | t <sub>d(off)</sub>    | V <sub>GS</sub> =                                                    | = 10 V, R <sub>g</sub> =               | 9.1 Ω                     | -    | 68   | 102   | ns   |

| Fall Time                                                  | t <sub>f</sub>         |                                                                      |                                        |                           | -    | 42   | 84    | 1    |

| Gate Input Resistance                                      | R <sub>g</sub>         | f = 1 MHz, open drain                                                |                                        | -                         | 0.78 | -    | Ω     |      |

| Drain-Source Body Diode Characteristic                     |                        |                                                                      |                                        |                           |      |      |       |      |

| Continuous Source-Drain Diode Current                      | ١ <sub>S</sub>         | MOSFET sym<br>showing the                                            | MOSFET symbol showing the              |                           | -    | -    | 21    |      |

| Pulsed Diode Forward Current                               | I <sub>SM</sub>        | integral reverse<br>p - n junction diode                             |                                        | -                         | -    | 53   | A     |      |

| Diode Forward Voltage                                      | V <sub>SD</sub>        | T <sub>J</sub> = 25 °C, I <sub>S</sub> = 11 A, V <sub>GS</sub> = 0 V |                                        | -                         | 0.9  | 1.2  | V     |      |

| Reverse Recovery Time                                      | t <sub>rr</sub>        |                                                                      |                                        |                           | -    | 160  | -     | ns   |

| Reverse Recovery Charge                                    | Q <sub>rr</sub>        | $T_J = 2$                                                            | 5 °C, I <sub>F</sub> = I <sub>S</sub>  | = 11 A,                   | -    | 1.2  | -     | μ    |

| Reverse Recovery Current                                   | I <sub>RRM</sub>       | di/dt =                                                              | 100 A/µs, V                            | <sub>R</sub> = 25 V       | -    | 14   |       | A    |

Notes

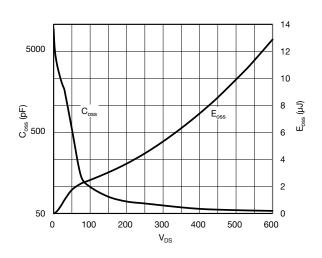

a.  $C_{oss(er)}$  is a fixed capacitance that gives the same energy as  $C_{oss}$  while  $V_{DS}$  is rising from 0 % to 80 %  $V_{DSS}$ . b.  $C_{oss(tr)}$  is a fixed capacitance that gives the same charging time as  $C_{oss}$  while  $V_{DS}$  is rising from 0 % to 80 %  $V_{DSS}$ .

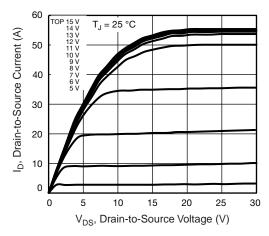

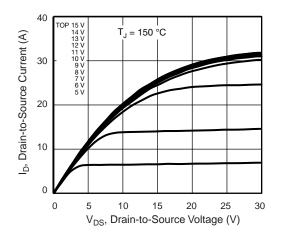

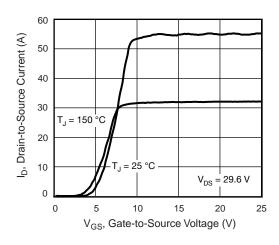

#### TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

Fig. 1 - Typical Output Characteristics

Fig. 2 - Typical Output Characteristics

Fig. 3 - Typical Transfer Characteristics

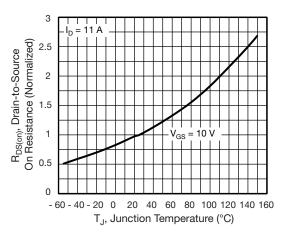

Fig. 4 - Normalized On-Resistance vs. Temperature

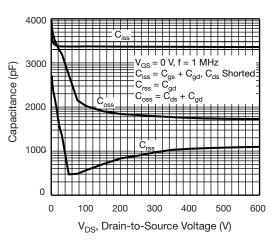

Fig. 5 - Typical Capacitance vs. Drain-to-Source Voltage

Fig. 6 -  $C_{oss}$  and  $E_{oss}$  vs.  $V_{DS}$

### **VBZMB18N65**

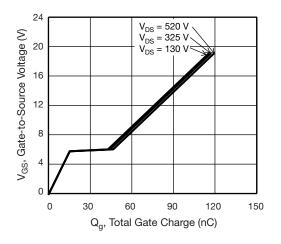

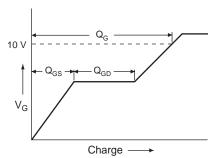

Fig. 7 - Typical Gate Charge vs. Gate-to-Source Voltage

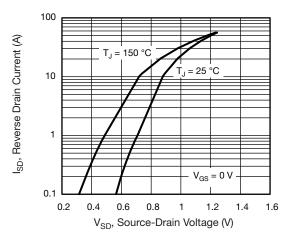

Fig. 8 - Typical Source-Drain Diode Forward Voltage

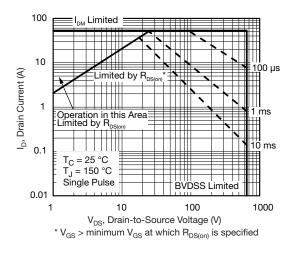

Fig. 9 - Maximum Safe Operating Area

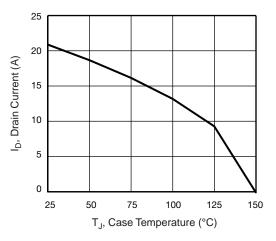

Fig. 10 - Maximum Drain Current vs. Case Temperature

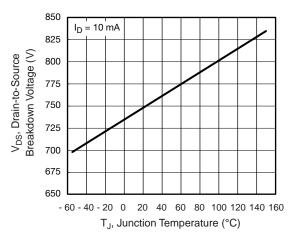

Fig. 11 - Temperature vs. Drain-to-Source Voltage

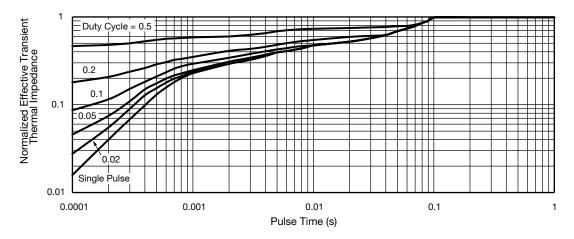

Fig. 12 - Normalized Thermal Transient Impedance, Junction-to-Case

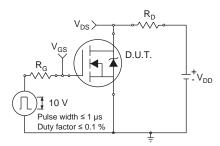

Fig. 13 - Switching Time Test Circuit

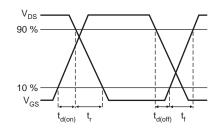

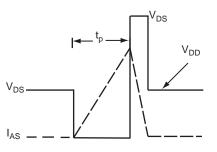

Fig. 14 - Switching Time Waveforms

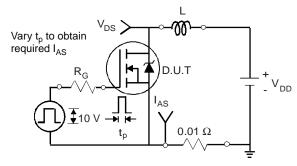

Fig. 15 - Unclamped Inductive Test Circuit

Fig. 16 - Unclamped Inductive Waveforms

Fig. 17 - Basic Gate Charge Waveform

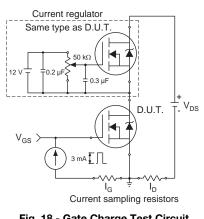

Fig. 18 - Gate Charge Test Circuit

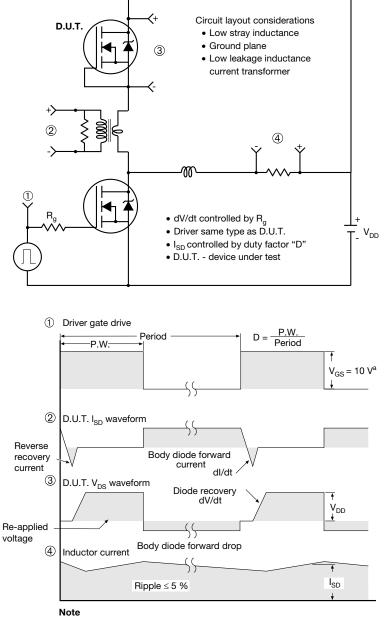

#### Peak Diode Recovery dV/dt Test Circuit

a.  $V_{GS} = 5$  V for logic level devices

Fig. 19 - For N-Channel

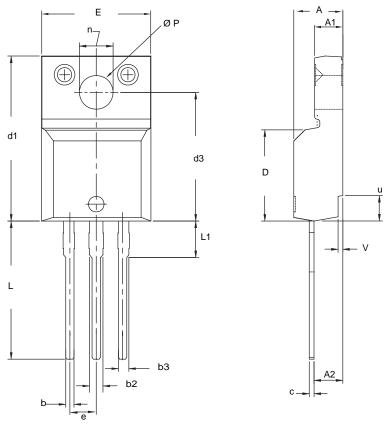

#### **TO-220 FULLPAK (HIGH VOLTAGE)**

| DIM. | MILLI    | METERS | INCHES    |       |  |

|------|----------|--------|-----------|-------|--|

|      | MIN.     | MAX.   | MIN.      | MAX.  |  |

| А    | 4.570    | 4.830  | 0.180     | 0.190 |  |

| A1   | 2.570    | 2.830  | 0.101     | 0.111 |  |

| A2   | 2.510    | 2.850  | 0.099     | 0.112 |  |

| b    | 0.622    | 0.890  | 0.024     | 0.035 |  |

| b2   | 1.229    | 1.400  | 0.048     | 0.055 |  |

| b3   | 1.229    | 1.400  | 0.048     | 0.055 |  |

| С    | 0.440    | 0.629  | 0.017     | 0.025 |  |

| D    | 8.650    | 9.800  | 0.341     | 0.386 |  |

| d1   | 15.88    | 16.120 | 0.622     | 0.635 |  |

| d3   | 12.300   | 12.920 | 0.484     | 0.509 |  |

| E    | 10.360   | 10.630 | 0.408     | 0.419 |  |

| е    | 2.54 BSC |        | 0.100 BSC |       |  |

| L    | 13.200   | 13.730 | 0.520     | 0.541 |  |

| L1   | 3.100    | 3.500  | 0.122     | 0.138 |  |

| n    | 6.050    | 6.150  | 0.238     | 0.242 |  |

| ØP   | 3.050    | 3.450  | 0.120     | 0.136 |  |

| u    | 2.400    | 2.500  | 0.094     | 0.098 |  |

| V    | 0.400    | 0.500  | 0.016     | 0.020 |  |

#### Notes

1. To be used only for process drawing. 2. These dimensions apply to all TO-220, FULLPAK leadframe versions 3 leads. 3. All critical dimensions should C meet  $C_{pk} > 1.33$ . 4. All dimensions include burrs and plating thickness. 5. No chipping or package damage.

# Disclaimer

All products due to improve reliability, function or design or for other reasons, product specifications and data are subject to change without notice.

Taiwan VBsemi Electronics Co., Ltd., branches, agents, employees, and all persons acting on its or their representatives (collectively, the "Taiwan VBsemi"), assumes no responsibility for any errors, inaccuracies or incomplete data contained in the table or any other any disclosure of any information related to the product.(www.VBsemi.com)

Taiwan VBsemi makes no guarantee, representation or warranty on the product for any particular purpose of any goods or continuous production. To the maximum extent permitted by applicable law on Taiwan VBsemi relinquished: (1) any application and all liability arising out of or use of any products; (2) any and all liability, including but not limited to special, consequential damages or incidental; (3) any and all implied warranties, including a particular purpose, non-infringement and merchantability guarantee.

Statement on certain types of applications are based on knowledge of the product is often used in a typical application of the general product VBsemi Taiwan demand that the Taiwan VBsemi of. Statement on whether the product is suitable for a particular application is non-binding. It is the customer's responsibility to verify specific product features in the products described in the specification is appropriate for use in a particular application. Parameter data sheets and technical specifications can be provided may vary depending on the application and performance over time. All operating parameters, including typical parameters must be made by customer's technical experts validated for each customer application. Product specifications do not expand or modify Taiwan VBsemi purchasing terms and conditions, including but not limited to warranty herein.

Unless expressly stated in writing, Taiwan VBsemi products are not intended for use in medical, life saving, or life sustaining applications or any other application. Wherein VBsemi product failure could lead to personal injury or death, use or sale of products used in Taiwan VBsemi such applications using client did not express their own risk. Contact your authorized Taiwan VBsemi people who are related to product design applications and other terms and conditions in writing.

The information provided in this document and the company's products without a license, express or implied, by estoppel or otherwise, to any intellectual property rights granted to the VBsemi act or document. Product names and trademarks referred to herein are trademarks of their respective representatives will be all.

# **Material Category Policy**

Taiwan VBsemi Electronics Co., Ltd., hereby certify that all of the products are determined to be RoHS compliant and meets the definition of restrictions under Directive of the European Parliament 2011/65 / EU, 2011 Nian. 6. 8 Ri Yue restrict the use of certain hazardous substances in electrical and electronic equipment (EEE) - modification, unless otherwise specified as inconsistent.(www.VBsemi.com)

Please note that some documents may still refer to Taiwan VBsemi RoHS Directive 2002/95 / EC. We confirm that all products identified as consistent with the Directive 2002/95 / EC European Directive 2011/65 /.

Taiwan VBsemi Electronics Co., Ltd. hereby certify that all of its products comply identified as halogen-free halogen-free standards required by the JEDEC JS709A. Please note that some Taiwanese VBsemi documents still refer to the definition of IEC 61249-2-21, and we are sure that all products conform to confirm compliance with IEC 61249-2-21 standard level JS709A.